### (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2018/0191539 A1

### Jul. 5, 2018 (43) **Pub. Date:**

#### (54) ENERGY EFFICIENT HIGHWAY ADDRESSABLE REMOTE TRANSDUCER COHERENT 8-ARY PHASE SHIFT KEYING **MODEM**

(71) Applicant: Pranatharthi Subbaratnam Haran,

Fremont, CA (US)

(72)Inventor: Pranatharthi Subbaratnam Haran,

Fremont, CA (US)

Appl. No.: 15/905,786 (21)

(22) Filed: Feb. 26, 2018

#### Related U.S. Application Data

(63) Continuation-in-part of application No. 15/294,680, filed on Oct. 15, 2016.

#### **Publication Classification**

(51) Int. Cl. H04L 27/20 (2006.01) (52) U.S. Cl. CPC ...... *H04L 27/20* (2013.01)

#### (57)ABSTRACT

A method and a highway addressable remote transducer (HART) modem for modulating and demodulating an analog signal including a HART message are provided. With low power consumption, the less computationally intensive HART modem modulates the analog signal using a coherent 8-ary phase shift keying (C8PSK) technique with a predefined gray code lookup table and a pre-generated sample lookup table having phase modulated digital signals indexed by index vectors, and transmits a HART C8PSK analog signal to sensor devices. A C8PSK demodulator in the HART modem demodulates the HART C8PSK analog signal by performing coarse estimation and fine estimation of phase errors and by estimation of a timing offset using a decision estimator. An automatic modulation classifier of the C8PSK demodulator validates presence of the analog signal in a C8PSK protocol by determining signs of in-phase and quadrature phase signals corresponding to each subsequent processed digitized sample of the analog signal.

FIG. 1 (Prior Art)

FIG. 2 (Prior Art)

FIG. 3 (Prior Art)

FIG. 5

| GRAY<br>CODED<br>SYMBOL | TRIBIT<br>VALUE | C8PSK OUTPUT PHASE FOR THE GRAY CODED SYMBOL | 407          |

|-------------------------|-----------------|----------------------------------------------|--------------|

| 0                       | 000             | -112.5°                                      |              |

| 1                       | 001             | -157.5°                                      | <del>-</del> |

| 2                       | 010             | -67.5°                                       | _            |

| 3                       | 011             | -22.5°                                       |              |

| 4                       | 100             | +112.5°                                      |              |

| 5                       | 101             | +157.5°                                      |              |

| 6                       | 110             | +67.5°                                       |              |

| 7                       | 111             | +22.5°                                       |              |

FIG. 6

**FIG. 7**

SAMPLE SAMPLE SAMPLE # SYMBOL SYMBOL SYMBOL 2 2 SYMBOL SYMBOL SYMBOL SYMBOL SYMBOL O 1 1 1 1

FIG. 8

FIG. 9A

FIG. 9B

**FIG. 9C**

**FIG. 10**

FIG. 12

**FIG. 13**

**FIG. 14**

**FIG. 15**

**FIG. 16**

**FIG. 17**

**FIG. 18**

FIG. 19

#### ENERGY EFFICIENT HIGHWAY ADDRESSABLE REMOTE TRANSDUCER COHERENT 8-ARY PHASE SHIFT KEYING MODEM

## CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is a continuation-in-part application of the non-provisional patent application titled "Energy Efficient Highway Addressable Remote Transducer C8PSK Modem", application Ser. No. 15/294,680, filed in the United States Patent and Trademark Office on Oct. 15, 2016. The specification of the above referenced patent application is incorporated herein by reference in its entirety.

#### BACKGROUND

[0002] Smart field data devices in use today are generally Highway Addressable Remote Transducer (HART) enabled devices. HART is a global standard for sending and receiving digital information across analog wires between smart devices and control or monitoring systems. The HART communications protocol is widely recognized as the industry standard for digitally enhanced 4 milliamperes (mA) to 20 mA smart instrument communication. Use of HART based technology is growing rapidly and most major global instrumentation suppliers offer products with the HART communications protocol. The HART communications protocol enables two-way digital communication with smart instruments without disturbing 4 mA-20 mA analog signals. The HART communications protocol utilizes, for example, the Bell 202 frequency shift keying (FSK) standard of the Bell 202 modulator-demodulator (modem) of Bell System to superimpose digital communication signals at a low level over the 4 mA-20 mA analog signals. HART technology enables two-way field communication and makes it possible for additional information beyond typical process variables to be communicated to and from a smart field instrument. Current deployment of HART field data devices, that is, smart field data devices that support the HART protocol, utilize a hardware based Bell 202 modem at 1200 bits per second and a separate microcontroller for an implementation of the HART communications protocol. There are a number of hardware based modems that use a Bell 202 based modulation scheme, available in the industry. A HART field data device comprises a microcontroller, a HART modem, and an interface arrangement compliant to a conventional 4 mA-20 mA current loop circuit. The HART modem supporting the HART FSK protocol demodulates a non-coherent HART FSK signal by mixing the non-coherent HART FSK signal with a free running oscillator, that is, a carrier signal, and then identifies a phase of a resultant signal. The total component count of the HART modem to perform both modulation and demodulation adds to the overall cost, lowers reliability of the HART modem, and results in high power consumption.

[0003] In 2001, the Highway Addressable Remote Transducer (HART) Communication Foundation (HCF) published a high speed HART (HSH) communication protocol at 9600 bits per second speed using a coherent 8-ary phase shift keying (C8PSK) modulation and demodulation scheme. The HSH communication protocol, that is, the HART C8PSK protocol caters for increasing the number of transactions between HART field data devices and control

and monitoring systems to realize multiple control functions of the HART field data devices. A physical layer specification of the HART C8PSK protocol specifies that physical device type, message structure, and network configuration rules of the HART C8PSK protocol are same as the physical layer specification of the HART frequency shift keying (FSK) protocol. That is, the HART field data devices can communicate using the HART C8PSK protocol and/or the HART FSK protocol. The HART field data devices employ a modem that functions for both the HART C8PSK protocol and the HART FSK protocol. The analog signals transmitted and received by the HART field data devices are HART C8PSK analog signals or HART FSK analog signals.

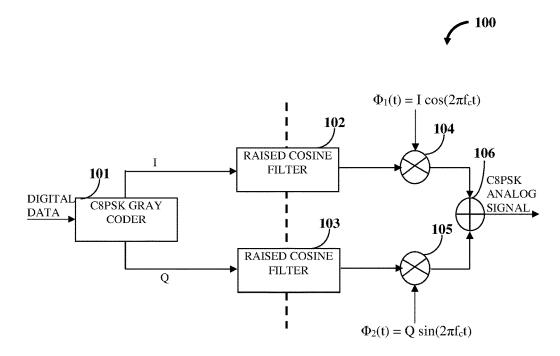

[0004] FIG. 1 (Prior Art) exemplarily illustrates a typical Highway Addressable Remote Transducer (HART) coherent 8-ary phase shift keying (C8PSK) modulator 100 comprising a C8PSK gray coder 101, raised cosine filters 102 and 103, and mixers 104, 105, and 106, for modulating an analog signal comprising a HART message transmitted by HART field data devices, that is, sensor devices in a field environment. The C8PSK gray coder 101 receives a serial data bit stream obtained on sampling of an analog signal output by the HART field data devices. The C8PSK gray coder 101 divides the received serial data bit stream into symbols comprising three consecutive bits of the serial data bit stream and maps each of the symbols to a phase angle. The C8PSK gray coder 101 also maps each of the phase angles to a corresponding in-phase component and a quadrature phase component. The HART C8PSK specifications further require that the in-phase component and the quadrature phase component be shaped using 50% raised cosine filters 102 and 103 to achieve minimal inter symbol interference. The in-phase component of each of the symbols is shaped through the raised cosine filter 102 and the quadrature phase component of each of the symbols is shaped through another raised cosine filter 103. The raised cosine filters 102 and 103 output an in-phase (I) signal and a quadrature phase (Q) signal corresponding to each of the symbols. The I signal and the Q signal are modulated using a carrier signal of frequency of, for example, 3200 hertz (Hz). The modulation comprises generating a HART C8PSK analog signal by multiplying the resulting output I signal of the raised cosine filter 102 by cos(w,t) to obtain a first product and subtracting a second product of the output Q signal of the raised cosine filter 103 and sin(w<sub>c</sub>t) from the first product using the mixers 104, 105, and 106. The HART C8PSK analog signal is represented below:

$X(t)=I\cos(w_c t)-Q\sin(w_c t)$

[0005] Consider an example where an output sample rate of the Highway Addressable Remote Transducer (HART) coherent 8-ary phase shift keying (C8PSK) analog signal of 25600 Hz is desired from the HART C8PSK modulator 100. For this output sample rate, the raised cosine filters 102 and 103, for example, finite impulse response filters in the HART C8PSK modulator 100 require 17 filter taps. Thus, the raised cosine filters 102 and 103 for the in-phase component and the quadrature phase component respectively, require 17 multiplications and 17 additions each. Further, the in-phase (I) signal and the quadrature phase (Q) signal require 2 more multiplications and an addition each in the mixers 104, 105, and 106. For transmitting one sample of the HART message in the carrier signal, the HART C8PSK modulator 100 involves 36 multiplications and 35

additions. Thus, for an output sample rate of the HART C8PSK analog signal of 25600 Hz, the HART C8PSK modulator 100 performs 921600 multiplications and 896000 additions. All these computations require large computing resources thus making it difficult to meet low power requirements of the HART C8PSK modulator 100 in transmission of analog signals. Therefore, there is a need for a HART C8PSK modem that performs modulation of the received analog signals with low power consumption.

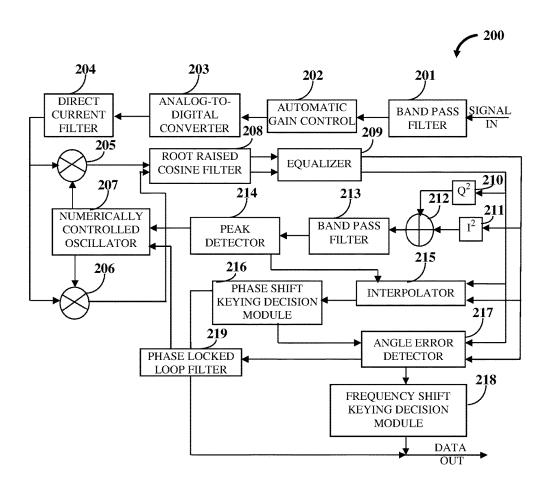

[0006] FIG. 2 (Prior Art) exemplarily illustrates a demodulator 200 of a multi-speed Highway Addressable Remote Transducer (HART) (MSH) modem jointly developed by industry majors such as Rosemount Inc., SMAR, Siemens Inc., and the HART Communication Foundation (HCF). The MSH modem comprises a modulator and the demodulator 200. To achieve power efficiency, both the modulator and the demodulator 200 of the MSH modem need to be optimized for power and performance. The demodulator 200 exemplarily illustrated in FIG. 2, is initialized as an incoming signal is a HART coherent 8-ary phase shift keying (C8PSK) analog signal even though the demodulator 200 can classify the incoming signal as a frequency shift keying (FSK) signal and demodulate the FSK signal. The demodulator 200 comprises band pass filters 201 and 213, an automatic gain control circuit 202, an analog-to-digital converter (ADC) 203, a direct current filter 204, mixers 205 and 206, a numerically controlled oscillator 207, a root raised cosine filter 208, an equalizer 209, squaring circuits 210 and 211, a summing circuit 212, a peak detector 214, an interpolator 215, a phase shift keying (PSK) decision module 216, an angle error detector 217, a phase locked loop filter 219, and a frequency shift keying (FSK) decision module 218. The band pass filter 201 filters the incoming signal. The automatic gain control circuit 202 adjusts gain of the incoming signal. The ADC 203 digitizes and converts the gain adjusted signal to digitized samples. The direct current filter 204 smoothens ripples in the digitized samples. In-phase components and quadrature phase components corresponding to the digitized samples are generated using the numerically controlled oscillator 207, the mixers 205 and 206, and the root raised cosine filter 208. The root raised cosine filter 208 is a pulse shaping filter for pulse shaping the generated in-phase components and the generated quadrature phase components to generate inphase signals and quadrature phase signals. The root raised cosine filter 208 also functions as a low pass filter to remove unwanted high frequencies in the generated in-phase components and the generated quadrature phase components.

[0007] The equalizer 209 receives the outputs of the root raised cosine filter 208 and generates delayed in-phase signals and delayed quadrature phase signals that are fed as inputs to a symbol synchronization circuit comprising a pair of squaring circuits 210 and 211. The squaring circuits 210 and 211 square the delayed in-phase signals and the delayed quadrature phase signals and the summing circuit 212 sums the result to produce a demodulated analog signal that is filtered by the band pass filter 213. The peak detector 214 detects peaks of the demodulated analog signal that correspond to sampling time instants of the Highway Addressable Remote Transducer (HART) coherent 8-ary phase shift keying (C8PSK) analog signal that is sampled by the analogto-digital converter (ADC) 203. The outputs of the equalizer 209 are fed to the interpolator 215 and the angle error detector 217. The interpolator 215 selects a digitized sample of the HART C8PSK analog signal that is to be unmapped and decoded to a symbol with binary bits by the phase shift keying (PSK) decision module 216. The angle error detector 217 identifies the protocol of the incoming signal, that is, whether the incoming signal is a frequency shift keying (FSK) signal or a C8PSK analog signal.

[0008] For demodulating the Highway Addressable Remote Transducer (HART) frequency shift keying (FSK) analog signals, the multi-speed HART (MSH) modem uses the equalizer 209 configured as an adaptive equalizer to compensate for cable losses in transmission since the HART FSK signals slightly distort during the transmission. For coherent demodulation of the HART coherent 8-ary phase shift keying (C8PSK) analog signal as per the physical layer specification of the HART C8PSK protocol, the demodulator 200 provides the automatic gain control (AGC) circuit 202, the root raised cosine filter 208, the symbol synchronization circuit, the equalizer 209, the angle error detector 217, and the phase locked loop filter 219 for carrier recovery and signal identification by the phase shift keying (PSK) decision module 216 and the FSK decision module 218 as exemplarily illustrated in FIG. 2. With the additional components to cater for identification and demodulation of both the HART FSK analog signal and the HART C8PSK analog signal, the MSH modem has low reliability with high power consumption. The high power consumption in the demodulator 200 because of the number of multiplications used per symbol demodulation, and multipliers of the demodulator 200 also result in a large area in the MSH modem. Total worst case current is substantially high, more than about 2 mA. Therefore, there is a need for a HART C8PSK modem that performs demodulation of received analog signals with low power consumption.

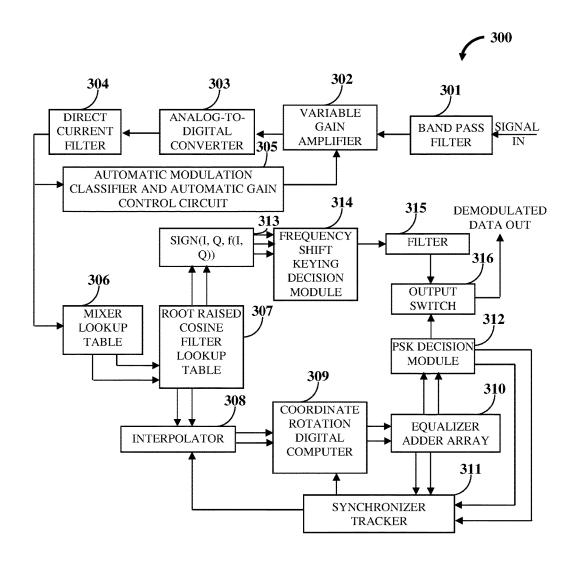

[0009] FIG. 3 (Prior Art) exemplarily illustrates a block diagram of a low power demodulator 300 of a multi-speed Highway Addressable Remote Transducer (HART) (MSH) modem. The low power demodulator 300 receives an incoming signal. The incoming signal is assumed to be a frequency shift keying (FSK) signal and the low power demodulator 300 is accordingly configured. The low power demodulator 300 comprises a band pass filter 301, a variable gain amplifier 302, an analog-to-digital converter (ADC) 303, a direct current filter 304, an automatic modulation classifier and automatic gain control circuit 305, a mixed lookup table 306, a root raised cosine filter lookup table 307, an interpolator 308, a coordinate rotation digital computer (CORDIC) 309, an equalizer adder array 310, a synchronizer tracker 311, a phase shift keying (PSK) decision module 312, an FSK decision module 314, a filter 315, and an output switch 316. The band pass filter 301 filters the incoming FSK signal. The variable gain amplifier 302 adjusts gain of the filtered FSK signal. The ADC 303 digitizes the gain adjusted FSK signal. The direct current filter 304 filters the digitized FSK signal. The automatic modulation classifier and the automatic gain control circuit 305 perform automatic modulation classification and automatic gain control. The automatic modulation classifier determines that the digitized samples of the gain adjusted signal are in the FSK protocol and demodulates the digitized samples using the mixer lookup table 306 and the raise cosine filter lookup table 307. Based on the sign 313 of the generated in-phase signal and the generated quadrature phase signal, the FSK decision module 314 outputs demodulated data through the output switch 316 via the filter 315 after carrier recovery. If the automatic modulation classifier determines that the digitized samples of the gain adjusted signal are in the coherent 8-ary phase shift keying (C8PSK) protocol, the interpolator 308, the CORDIC 309, and the equalizer adder array 310 in coordination with the synchronizer tracker 311 perform timing estimation of the digitized samples of the incoming C8PSK signal to output demodulated digitized samples. The equalizer adder array 310 initializes the synchronizer tracker 311 for a preamble of the HART message in the incoming C8PSK signal and functions as a fixed single preset equalizer that adapts to actual line conditions, that is, the digitized samples of the incoming C8PSK signal present in the low power demodulator 300 after initialization of the synchronizer tracker 311 is complete. Theoretically and in simulations, the low power demodulator 300 functions in accordance with requirements. In the low power demodulator 300 exemplarity illustrated in FIG. 3, the phase of the incoming C8PSK signal is estimated using the following equations:

$$\begin{split} & \operatorname{Sum} Q(m) = & \Sigma^{16}_{n=1} \ Q(n+m) \\ & \operatorname{Sum} I(m) = & \Sigma^{16}_{n=1} \ I(n+m) \\ & Ti(m) = & \Sigma^{8}_{n=1} \ I(n+m) - \Sigma^{15}_{n=8} \ I(n+m) \\ & \operatorname{Sum} Q(m) = & A \ \cos(\Delta\theta) \\ & \operatorname{Sum} I(m) = & A \ \sin(\Delta\theta) \end{split}$$

[0010] where  $\Delta\theta$  is a carrier phase error and is defined as  $\Delta\theta$ =45\*k+m, Q(n) is a quadrature phase component of the digitized samples of the received HART C8PSK analog signal, and I(n) is an in-phase component of the digitized samples of the received HART C8PSK analog signal. The resulting SumQ(m) and SumI(m) go through the phase shift keying (PSK) decision module 312, which judges the function parameter k and a lookup table of an abstract value SumQ(m) is used to compute m.

[0011] The low power demodulator 300 requires sampling of the received Highway Addressable Remote Transducer (HART) coherent 8-ary phase shift keying (C8PSK) analog signal at 8 times a baud rate of 3200 resulting in a substantially high sampling rate of more than 25 kilohertz (KHz). Another requirement of the multi-speed HART (MSH) modem is to get the low power demodulator 300 in an optimum detection range within a period of 40 symbols or bauds. To achieve this, a fast detection of an incoming phase of the received HART C8PSK analog signal and an estimation of a center point timing of an impulse response, that is, a I/Q waveform of root raised cosine filters in the low power demodulator 300 must be performed. Using the above equations, the low power demodulator 300 requires a substantially high sample rate of 25600 Hz to achieve the above recited requirement. To arrive at an accurate phase error estimate and an estimate of a timing offset, the low power demodulator 300 requires the high sample rate of 25600 Hz. The computing requirements of a processor of the MSH modem increase 2 times despite avoiding the use of multipliers. Moreover, the number of computing cycles is a major contributor to the computing requirements. Power consumption of the analog-to-digital converter (ADC) 303 is also increased by 50%. On experimenting, the phase error estimate and the estimate of the timing offset of the analog signal are found to be inaccurate most of the time.

[0012] Selection of coefficients of the equalizer in the low power demodulator 300 is performed for reducing a computing rate of the equalizer to minimize power consumption of the low power demodulator 300. An algorithm where a single predetermined equalizer is selected and a timing estimator based on Gardner's algorithm is disclosed below:

```

eT(nT) = I_p(nT) * [I((n+\frac{1}{2})T) - I((n-\frac{1}{2})T)] + Q_p(nT) * [Q \\ ((n+\frac{1}{2})T) - Q((n-\frac{1}{2})T)]

```

[0013] The algorithm is used to estimate the timing offset in the received analog signal. The estimated timing offset is fed back to the interpolator 308 as exemplarily illustrated in FIG. 3, where the interpolator 308 works twice per symbol as shown in the equation below:

$$eC(nT)=I_{D}(nT)*Q(nT)-I(nT)*Q_{D}(nT)$$

[0014] However, in practice, convergence of the equalizer and proper demodulation of the signal are not always successful. The algorithm above and the interpolator 308 are computationally more intensive. The low power demodulator 300 in the multi-speed Highway Addressable Remote Transducer (HART) (MSH) modem minimizes the number of multiplications needed by in-built algorithms for demodulation of the received HART frequency shift keying (FSK) signal or the received HART coherent 8-ary phase shift keying (C8PSK) analog signal. However, power consumption and cost of implementation of the MSH modem are not reduced. Demodulator structures with configurable filters and oscillators can demodulate the received HART FSK signal or the received HART C8PSK analog signal. However, the power consumption is not low. Furthermore, it is difficult to implement C8PSK modems in application specific integrated circuits (ASICs) that typically implement modems, because the existing C8PSK modem algorithms are too complex to implement in ASICS due to a multi-stage decision making process.

[0015] Typically, the Highway Addressable Remote Transducer (HART) coherent 8-ary phase shift keying (C8PSK) modem must perform simultaneous detection of the received analog signal in the frequency shift keying (FSK) protocol, that is, detection of the slower 1200 bits per second Bell 202 based FSK modulation signal, along with the received analog signal in the C8PSK protocol. The simultaneous detection is conventionally implemented by one of many automatic modulation classification (AMC) methods. Many of the AMC methods are computationally intensive and need to be performed at a high sample rate. In the low power demodulator 300 of the multi-speed Highway Addressable Remote Transducer (HART) (MSH) modem exemplarily illustrated in FIG. 3, detection of the analog signal in the FSK protocol is performed and then the low power demodulator 300 is switched to demodulate the analog signal in the C8PSK protocol, which is computationally intensive.

[0016] Although modulation is inherently less complex, efficiencies can be achieved in the modulator of the Highway Addressable Remote Transducer (HART) coherent 8-ary phase shift keying (C8PSK) modem too. Hence, to improve power efficiency in the HART C8PSK modem, there is a long felt but unresolved need for modulation and demodulation of the received analog signal to be optimized for power and performance. Moreover, there is a need for a demodulator in the HART C8PSK modem that identifies and

adaptively demodulates the received analog signal in the FSK protocol and the C8PSK protocol with low power consumption.

#### SUMMARY OF THE INVENTION

[0017] This summary is provided to introduce a selection of concepts in a simplified form that are further disclosed in the detailed description of the invention. This summary is not intended to determine the scope of the claimed subject matter

[0018] The method and the Highway Addressable Remote Transducer (HART) coherent 8-ary phase shift keying (C8PSK) modem, hereafter referred to as a "HART modem", disclosed herein address the above recited need for optimizing modulation and demodulation of a received analog signal in a C8PSK protocol comprising a HART message for power and performance. Moreover, the method and the HART modem disclosed herein address the above recited need for a demodulator that identifies and adaptively demodulates the received analog signal in the FSK protocol and the C8PSK protocol with low power consumption.

[0019] The method and the Highway Addressable Remote Transducer (HART) modem disclosed herein are used in a field environment and achieve a high level of efficiencies in both a modulator and a demodulator of the HART modem. The method disclosed herein employs the HART modem for modulating and transmitting an analog signal comprising a HART message to one or more sensor devices. The method and the HART modem disclosed herein provide a two-step estimation method for phase error estimation of the incoming coherent 8-ary phase shift keying (C8PSK) signal, that is, the incoming analog signal in the C8PSK protocol. The HART modem disclosed herein comprises a decision estimator for performing estimation of a timing offset along with phase error estimation and equalizer selection.

[0020] The Highway Addressable Remote Transducer (HART) modem disclosed herein achieves a high level of efficiencies in both modulation and demodulation of an analog signal. The HART modem transmits the HART coherent 8-ary phase shift keying (C8PSK) analog signal, that is, the analog signal in the C8PSK protocol comprising the HART message, and receives and demodulates the C8PSK analog signal to a digital signal using either a frequency shift keying (FSK) technique or a C8PSK technique.

[0021] For modulating the received analog signal, the Highway Addressable Remote Transducer (HART) modem performs the method steps of pre-calculating waveforms, hereafter referred to as "phase modulated digital signals", in a pre-generated sample lookup table, generating the pregenerated sample lookup table, and performing a lookup of the pre-generated sample lookup table to determine the phase modulated digital signals indexed by the index vectors. The pre-generated sample lookup table comprising the pre-calculated phase modulated digital signals is stored in a non-volatile memory or a non-transitory computer readable storage medium of a microcontroller of the HART modem. In generating the pre-generated sample lookup table, the HART modem limits other phase modulated digital signals from being pre-calculated using a requirement where frequency of a carrier signal to be used for modulating the received analog signal is specified as 3200 hertz (Hz) and a baud rate of the transmitted analog signal, that is, the HART coherent 8-ary phase shift keying (C8PSK) analog signal is specified as 3200. As phase of a sine wave is the same after each baud of the HART C8PSK analog signal and the sine wave repeats itself, the size of the pre-generated sample lookup table is minimized, for example, to a few kilobytes, thereby avoiding use of larger memory as used in a conventional HART modem.

[0022] In the method disclosed herein, the Highway Addressable Remote Transducer (HART) modem for modulating and transmitting an analog signal comprising a HART message to one or more sensor devices is provided. The HART modem disclosed herein comprises multiple analogto-digital converters (ADCs), a parallel-to-serial converter, a gray coder, a coherent phase shift keying modulator, a digital-to-analog converter (DAC), at least one microcontroller configured to execute computer program instructions for operating the HART modem, and a non-transitory computer readable storage medium for storing a predefined gray code lookup table and a pre-generated sample lookup table. One of the ADCs receives and converts the analog signal into digitized samples by sampling and digitizing the received analog signal at a sampling rate. The parallel-toserial converter converts the HART message in the digitized samples into serial data bit streams. The serial data bit streams comprise binary information. The gray coder divides each of the serial data bit streams into symbols and gray codes the symbols using the predefined gray code lookup table. Each of the symbols comprises a predetermined number of consecutive bits in each of the serial data bit streams and represents a predetermined number of the digitized samples.

[0023] The microcontroller of the Highway Addressable Remote Transducer (HART) modem generates an index vector of the pre-generated sample lookup table for indexing a phase modulated digital signal in the pre-generated sample lookup table by grouping a predetermined number of the gray coded symbols and the predetermined number of the digitized samples. The microcontroller further determines a phase modulated digital signal in the pre-generated sample lookup table, corresponding to the generated index vector of the pre-generated sample lookup table for reducing power intensive computations in phase modulation by the coherent phase shift keying modulator of the HART modem. The digital-to-analog converter (DAC) converts the determined phase modulated digital signal to a phase modulated analog signal and transmits the phase modulated analog signal comprising the HART message to one or more sensor devices via a serial peripheral interface of the HART modem. The transmitted phase modulated analog signal is in the coherent 8-ary phase shift keying (C8PSK) protocol.

[0024] The microcontroller of the Highway Addressable Remote Transducer (HART) modem determines in-phase components and quadrature phase components of pre-gray coded symbols corresponding to analog signals received by the HART modem by mapping the pre-gray coded symbols to predetermined phase angles in the predefined gray code lookup table. The coherent phase shift keying modulator comprises root raised cosine filters and mixers. The root raised cosine filters of the coherent phase shift keying modulator pulse shape the determined in-phase components and the determined quadrature phase components of the pre-gray coded symbols corresponding to the received analog signal. The mixers of the coherent phase shift keying modulator modulate the pulse shaped in-phase components and the pulse shaped quadrature phase components with a

carrier signal for generating phase modulated digital signals. The microcontroller stores the generated phase modulated digital signals in the pre-generated sample lookup table. The microcontroller generates the pre-generated sample lookup table using the pre-gray coded symbols based on a frequency of the carrier signal being in synchronization with a baud rate of a phase modulated analog signal to be transmitted to one or more sensor devices.

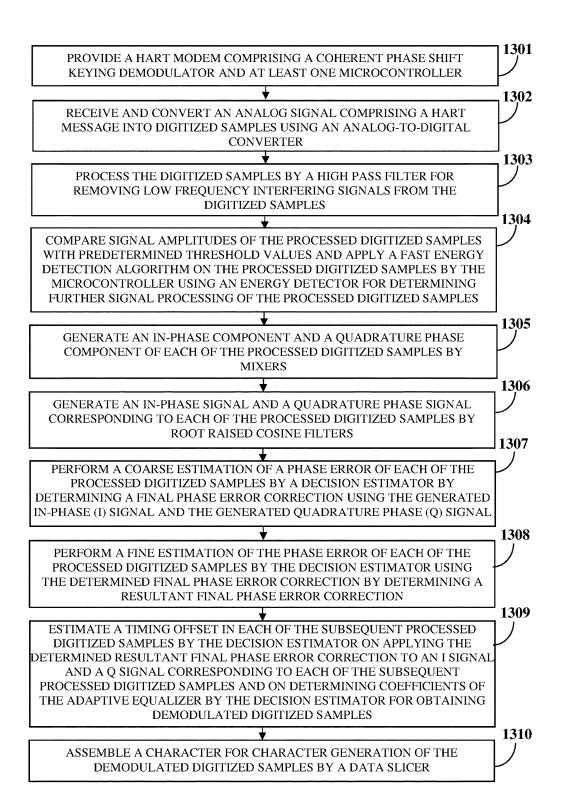

[0025] Also, disclosed herein is a method for demodulating an analog signal comprising a Highway Addressable Remote Transducer (HART) message. In the method disclosed herein, the HART modem comprising a coherent phase shift keying demodulator is provided. The coherent phase shift keying demodulator comprises multiple analogto-digital converters (ADCs), a high pass filter, an energy detector, mixers, root raised cosine filters, a decision estimator, an adaptive equalizer, and a data slicer. One of the ADCs of the coherent phase shift keying demodulator receives and converts an analog signal comprising the HART message into digitized samples by sampling and digitizing the received analog signal at a sampling rate. The high pass filter processes the digitized samples for removing low frequency interfering signals from the digitized samples. The microcontroller compares signal amplitudes of the processed digitized samples with predetermined threshold values and applies a fast energy detection algorithm on the processed digitized samples using the energy detector for determining further signal processing of the processed digi-

[0026] The mixers of the coherent phase shift keying demodulator generate an in-phase component and a quadrature phase component of each of the processed digitized samples by mixing each of the processed digitized samples with an in-phase carrier signal and a quadrature phase carrier signal respectively. The root raised cosine filters of the coherent phase shift keying demodulator generate an inphase signal and a quadrature phase signal corresponding to each of the processed digitized samples by pulse shaping the generated in-phase component and the generated quadrature phase component of each of the processed digitized samples respectively. The coherent phase shift keying demodulator detects the phase of the received analog signal, that is, the coherent 8-ary phase shift keying (C8PSK) analog signal in an optimum detection range, that is, within a period of 40 bauds or symbols. The coherent phase shift keying demodulator performs a fast detection of the incoming phase of the received C8PSK analog signal and estimates a centre point timing of the in-phase signal and the quadrature phase signal corresponding to each of the processed digitized samples. The coherent phase shift keying demodulator uses a twostage phase error estimation method followed by estimation of a timing offset and optimum equalizer selection. The two-stage phase error estimation comprising a coarse estimation of a phase error and a fine estimation of the phase error, starts after sufficient energy is detected in the processed digitized samples by the energy detector.

[0027] The decision estimator of the coherent phase shift keying demodulator performs a coarse estimation of a phase error of each of the processed digitized samples by determining a final phase error correction using the generated in-phase signal and the quadrature phase signal corresponding to each of the processed digitized samples. The decision estimator further performs a fine estimation of the phase error of each of the processed digitized samples using the

determined final phase error correction for determining a resultant final phase error correction. The decision estimator further determines coefficients of an adaptive equalizer of the Highway Addressable Remote Transducer (HART) modem and estimates a timing offset in each of the subsequent processed digitized samples for obtaining demodulated digitized samples. The subsequent processed digitized samples are the processed digitized samples of the received analog signal to which a resultant final phase error correction determined on performing the fine estimation of the phase error of each of the previously processed digitized samples is applied. The data slicer of the coherent phase shift keying demodulator assembles a character for character generation of the demodulated digitized samples. The HART modem demodulates the received analog signal in a frequency shift keying (FSK) protocol or demodulates the received analog signal in the coherent phase shift keying (C8PSK) protocol.

[0028] The coherent phase shift keying demodulator further comprises an automatic modulation classifier for detecting certain patterns in the coherent 8-ary phase shift keying (C8PSK) demodulated in-phase (I) signals and the quadrature phase (Q) signals, that is, the I signal and the Q signal corresponding to each of the processed digitized samples. The patterns are an indication of the presence of the received analog signal in the C8PSK protocol and by inference, an absence of the received analog signal in the Bell 202 frequency shift keying (FSK) protocol. When the absence of the received analog signal in the C8PSK protocol is asserted by the automatic modulation classifier, the coherent phase shift keying demodulator switches to a FSK demodulation method and detects the incoming FSK signal in time. The automatic modulation classifier validates presence of the received analog signal in the C8PSK protocol and absence of the received analog signal in the FSK protocol by determining signs of an I signal and a Q signal corresponding to each of the subsequent processed digitized samples, generated by the root raised cosine filters of the coherent phase shift keying demodulator, after performing the fine estimation of the phase error of each of the processed digitized samples and the estimation of the timing offset in each of the subsequent processed digitized samples.

[0029] Based on the Highway Addressable Remote Transducer (HART) coherent 8-ary phase shift keying (C8PSK) physical layer specification drafted by the HART Communication Foundation (HCF), after computing phase error estimates using the decision estimator of the coherent phase shift keying demodulator and applying the computed phase error estimates to the I signals and the Q signals of the subsequent processed digitized samples, the I signals corresponding to the subsequent processed digitized samples align with same polarity. The automatic modulation classifier avoids any further computational requirements and saves computing cycles and thus reduces power consumption of the HART modem. The coarse estimation of the phase error and the fine estimation of the phase error followed by estimation of the timing offset allow a lower sampling rate of 12800 Hz of the received analog signal and reduces computational complexity in the HART modem. The timing offset estimation in the HART modem is performed by mapping the subsequent processed digitized samples to one of 8 pre-selected equalizers. By implementing algorithms of low complexity and low computational

demands, the HART modem provides an improvement in HART C8PSK communications.

[0030] In one or more embodiments, related systems comprise circuitry and/or programming for effecting the methods disclosed herein. The circuitry and/or programming can be any combination of hardware, software, and/or firmware configured to effect the methods disclosed herein depending upon the design choices of a system designer. Also, in an embodiment, various structural elements can be employed depending on the design choices of the system designer.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0031] The foregoing summary, as well as the following detailed description of the invention, is better understood when read in conjunction with the appended drawings. For illustrating the invention, exemplary constructions of the invention are shown in the drawings. However, the invention is not limited to the specific methods and components disclosed herein. The description of a method step or a component referenced by a numeral in a drawing is applicable to the description of that method step or component shown by that same numeral in any subsequent drawing herein

[0032] FIG. 1 (Prior Art) exemplarily illustrates a typical Highway Addressable Remote Transducer coherent 8-ary phase shift keying modulator for modulating an analog signal comprising a Highway Addressable Remote Transducer message transmitted by Highway Addressable Remote Transducer field data devices in a field environment.

[0033] FIG. 2 (Prior Art) exemplarily illustrates a demodulator of a multi-speed Highway Addressable Remote Transducer modem.

[0034] FIG. 3 (Prior Art) exemplarily illustrates a block diagram of a low power demodulator of a multi-speed Highway Addressable Remote Transducer modem.

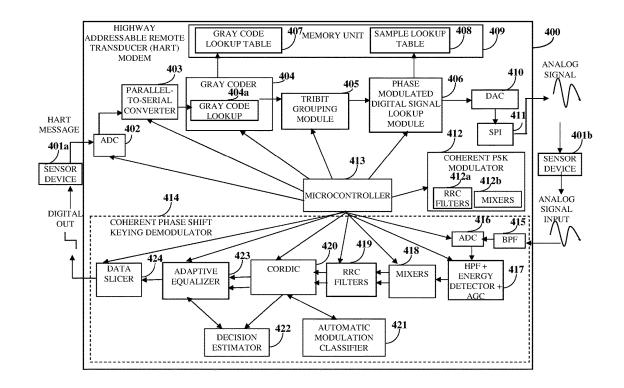

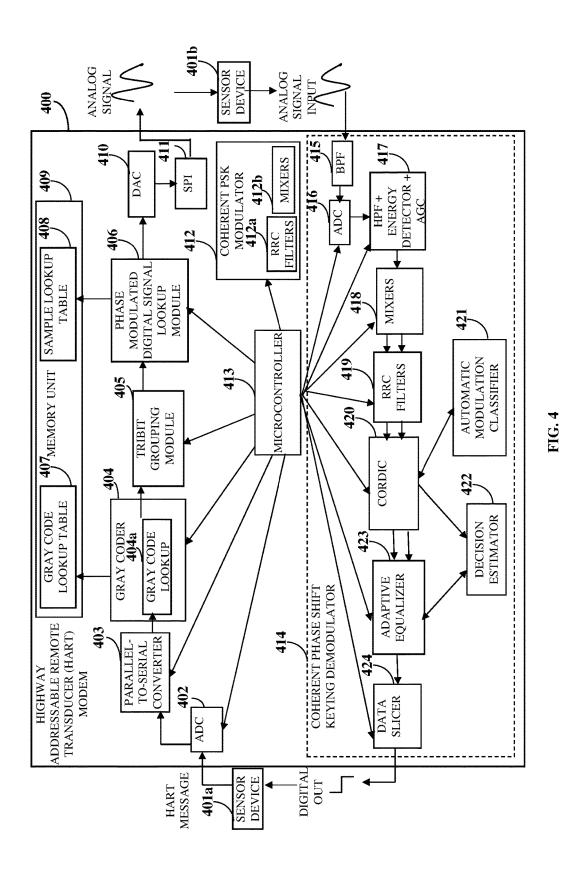

[0035] FIG. 4 exemplarily illustrates a block diagram of a Highway Addressable Remote Transducer modem.

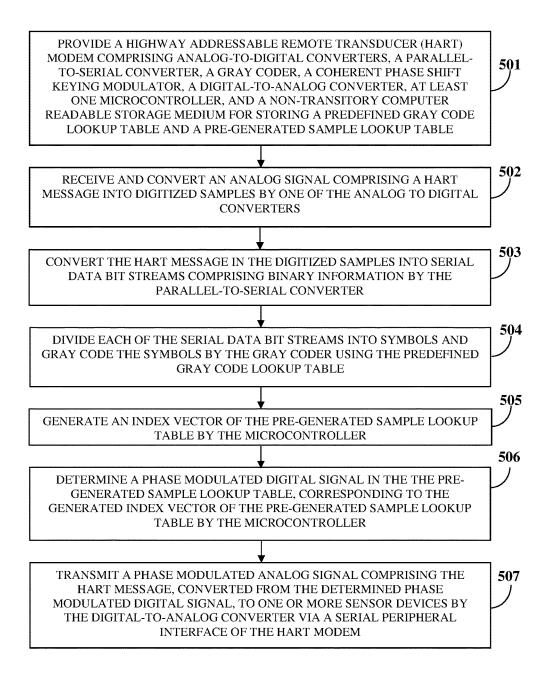

[0036] FIG. 5 illustrates a method for modulating and transmitting an analog signal comprising a Highway Addressable Remote Transducer message.

[0037] FIG. 6 exemplarily illustrates a predefined gray code lookup table of the Highway Addressable Remote Transducer modem.

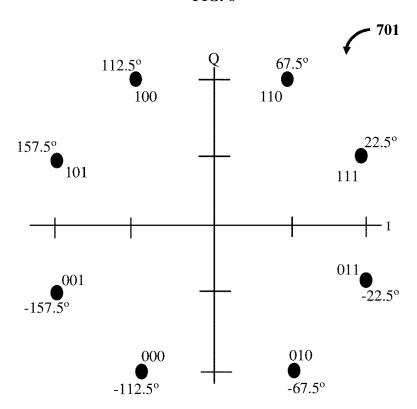

[0038] FIG. 7 exemplarily illustrates a constellation diagram corresponding to the predefined gray code lookup table shown in FIG. 6.

[0039] FIG. 8 exemplarily illustrates an index vector of a pre-generated sample lookup table.

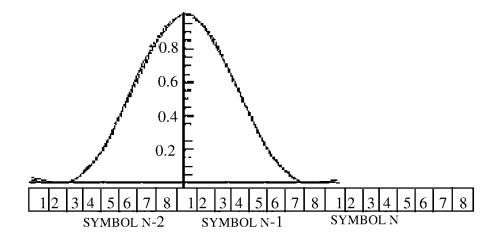

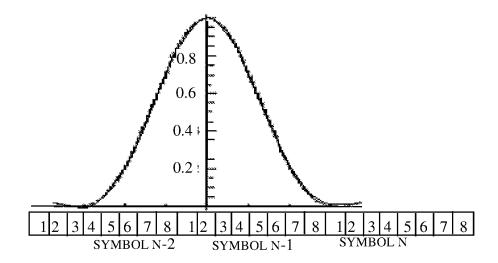

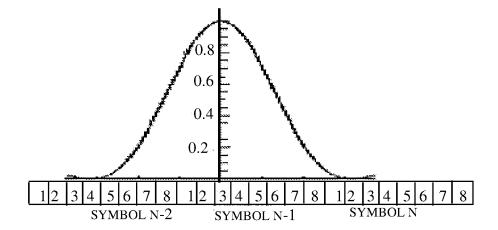

[0040] FIGS. 9A-9C exemplarily illustrate impulse responses of a root raised cosine filter of a coherent phase shift keying modulator of the Highway Addressable Remote Transducer modem.

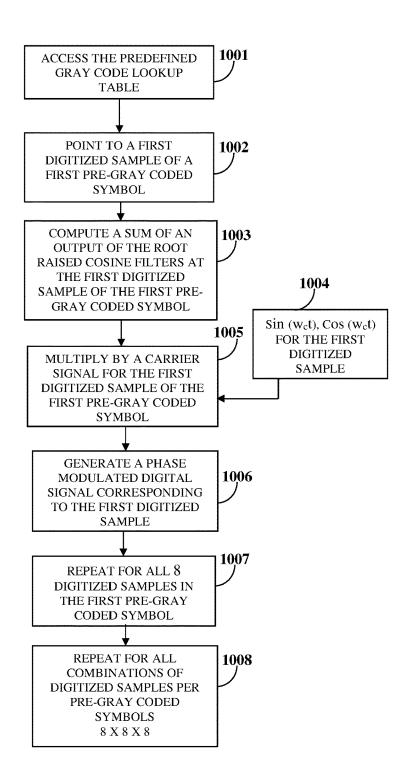

[0041] FIG. 10 exemplarily illustrates a flow chart comprising the steps performed by a microcontroller and the coherent phase shift keying modulator of the Highway Addressable Remote Transducer modem for generating a pre-generated sample lookup table.

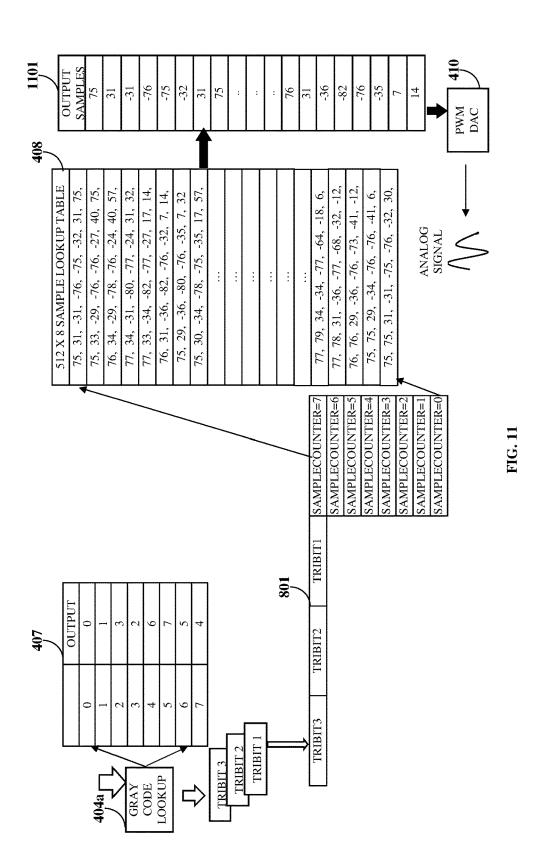

[0042] FIG. 11 exemplarily illustrates a schematic diagram showing modulation and transmission of an analog signal comprising a Highway Addressable Remote Transducer message performed by the Highway Addressable Remote Transducer modem.

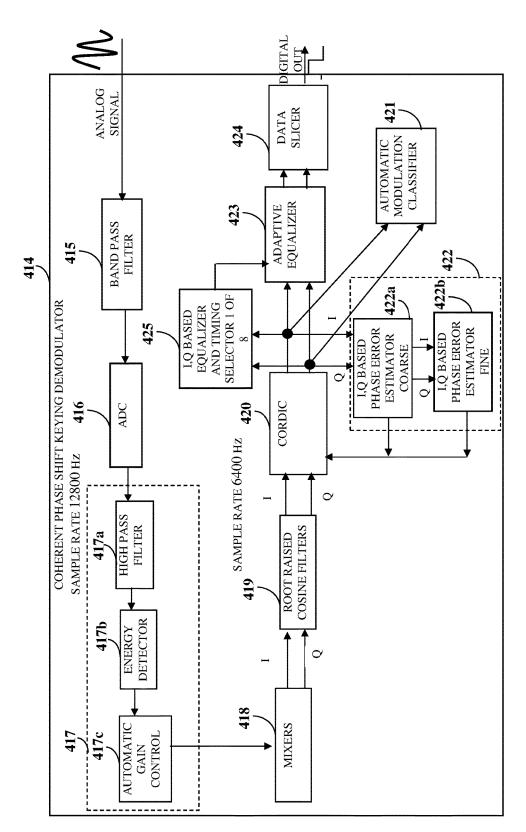

[0043] FIG. 12 exemplarily illustrates a block diagram of a coherent phase shift keying demodulator of the Highway

Addressable Remote Transducer modem for demodulating an analog signal comprising a Highway Addressable Remote Transducer message.

[0044] FIG. 13 illustrates a method for demodulating an analog signal comprising a Highway Addressable Remote Transducer message.

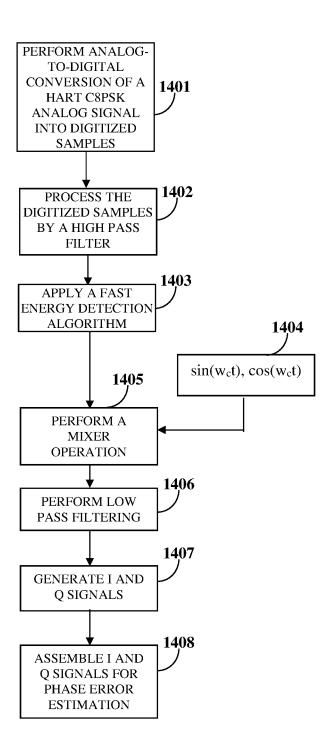

[0045] FIG. 14 exemplarily illustrates a flow diagram comprising the steps performed by the coherent phase shift keying demodulator of the Highway Addressable Remote Transducer modem for generating an in-phase signal and a quadrature phase signal corresponding to processed digitized samples.

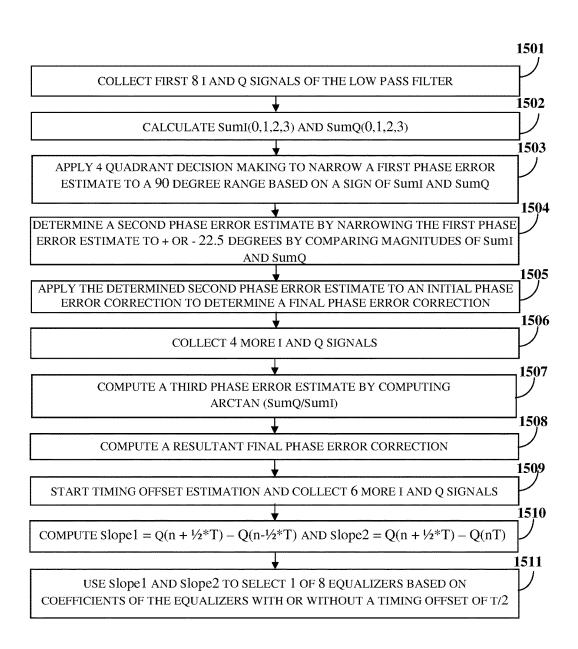

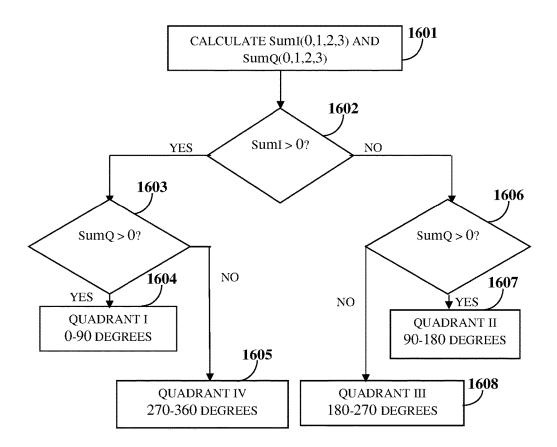

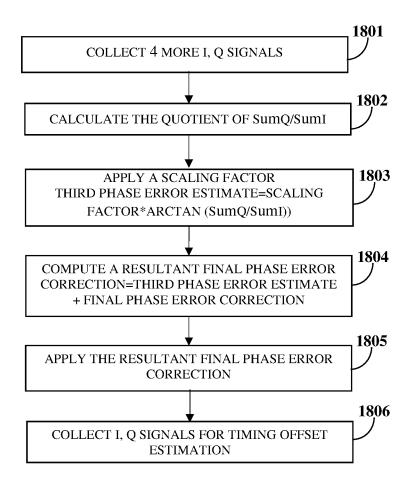

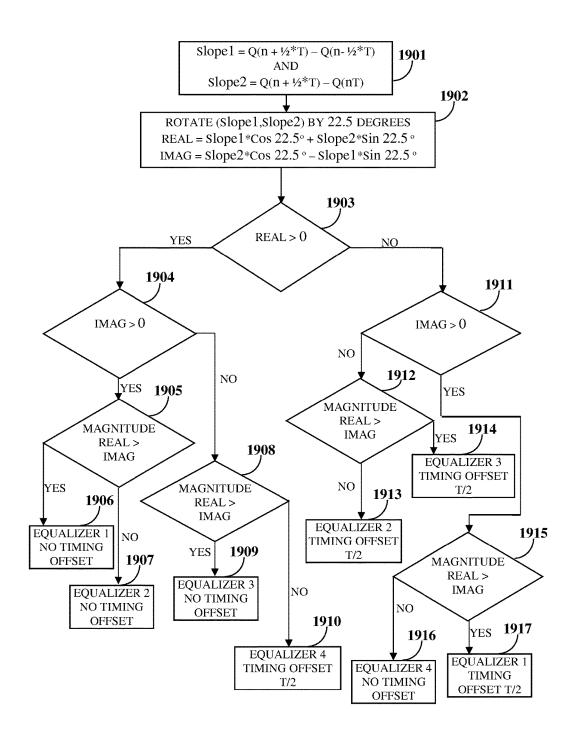

[0046] FIG. 15 exemplarily illustrates a flow diagram comprising the steps performed by a decision estimator of the coherent phase shift keying demodulator for performing a coarse estimation and a fine estimation of a phase error of each of processed digitized samples and for estimating a timing offset in each subsequent processed digitized sample. [0047] FIGS. 16-17 exemplarily illustrate flowcharts comprising the steps performed by the decision estimator of the coherent phase shift keying demodulator for performing a coarse estimation of a phase error of each of the processed digitized samples.

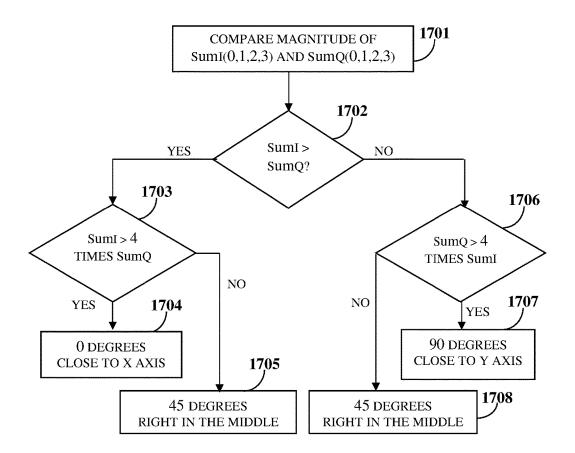

[0048] FIG. 18 exemplarily illustrates a flow diagram comprising the steps performed by the decision estimator of the coherent phase shift keying demodulator for performing a fine estimation of the phase error of each of the processed digitized samples.

[0049] FIG. 19 exemplarily illustrates a flowchart comprising the steps performed by the decision estimator of the coherent phase shift keying demodulator for determining coefficients of an equalizer and estimating a timing offset.

## DETAILED DESCRIPTION OF THE INVENTION

[0050] FIG. 4 exemplarily illustrates a block diagram of a Highway Addressable Remote Transducer (HART) modem 400. The HART modem 400 is a modem that performs modulation and demodulation of an analog signal in a HART coherent 8-ary phase shift keying (C8PSK) protocol. High speed smart sensor devices 401a and 401b use HART C8PSK modulation to transmit HART communication analog signals. The high speed HART C8PSK protocol is a communication protocol used worldwide in industrial applications, with majority of the smart sensor devices 401a and 401b and intelligent process measurement and control systems utilizing HART communication technology. The HART C8PSK protocol is a two-way communication protocol that caters for an increased number of transactions between the sensors devices 401a and 401b and control systems in an industrial application. The sensor devices 401a and 401b and the control systems communicate via 4 milliamperes (mA) to 20 mA analog signals that are modulated by C8PSK. The HART modem 400 also supports a HART frequency shift keying (FSK) protocol. In the HART FSK protocol, the HART modem 400 modulates the 4 mA-20 mA analog signal to frequencies of 1200 hertz (Hz) and 2200 Hz based on 0 bit and 1 bit in a HART message transmitted by a sensor device 401a or 401b.

[0051] The sensor devices 401a and 401b transmit analog data, for example, sensed parameters such as temperature, pressure, etc., and digital data representing, for example, identifiers (ID) of the sensor devices 401a and 401b as 4 mA-20 mA analog signals. The sensed parameters and the

digital data constitute the Highway Addressable Remote Transducer (HART) message in the 4 mA-20 mA analog signal. The HART modem 400 receives the 4 mA-20 mA analog signal comprising the HART message, superimposes the 4 mA-20 mA analog signal on a carrier signal, and transmits the superimposed signal as a phase modulated analog signal to a control system. In a phase shift keying technique, the phase of the carrier signal is shifted among possible phase angles, where each of the phase angles represents a predetermined number of bits. That is, in the coherent 8-ary phase shift keying (C8PSK) technique, the phase of the carrier signal is shifted among eight possible phase angles and each phase angle is represented by 3 bits. The phases of the analog signal comprising the HART message are eight possible phase angles. Similarly, the control system sends some operational instructions, for example, configuration settings, set points, etc., to the sensor devices 401a and 401b, in the form of analog signals over a pair of wires. The demodulation of the analog signals is performed by the HART modem 400 to extract the operational instructions, for example, the configuration settings, the set points, etc., from the analog signals. The operational instructions form the HART message that constitutes the analog signals. The HART message comprises four segments, namely, a preamble, a start flag, message data, and a stop flag. The preamble is a training sequence for training a demodulator of the HART modem 400. The start flag indicates beginning of a data segment of the HART message. The message data contains a normal HART frame representing the sensed parameters, the digital data, the operational instructions, etc. The stop flag indicates the end of the HART message.

[0052] The Highway Addressable Remote Transducer (HART) modem 400 disclosed herein comprises multiple analog-to-digital converters (ADCs), for example, 402, a parallel-to-serial converter 403, a gray coder 404, a coherent phase shift keying modulator 412, a digital-to-analog converter (DAC) 410, at least one microcontroller 413 configured to execute computer program instructions for operating the HART modem 400, and a non-transitory computer readable storage medium, that is, a memory unit 409 for storing a predefined gray code lookup table 407 and a pre-generated sample lookup table 408, for modulating a received analog signal. As used herein, "non-transitory computer readable storage medium" refers to all computer readable media, for example, non-volatile media, and transmission media, except for a transitory, propagating signal. Non-volatile media comprise, for example, solid state drives, optical discs or magnetic disks, and other persistent memory volatile media including a dynamic random access memory (DRAM), which typically constitute a main memory. Transmission media comprise, for example, coaxial cables, copper wire, fiber optic cables, modems, etc., including wires that constitute a system bus coupled to the microcontroller 413. The coherent phase shift keying modulator 412 comprises root raised cosine filters 412a and mixers 412b. The HART modem 400 transmits the phase modulated analog signal to the sensor device 401b via a serial peripheral interface (SPI) 411. The HART modem 400 further comprises a coherent phase shift keying demodulator 414 comprising multiple ADCs, for example, 416, a band pass filter 415, a module 417 with a high pass filter, an energy detector, an automatic gain control circuit, mixers 418, root raised cosine (RRC) filters 419, a coordinate rotation digital computer (CORDIC) 420, a decision estimator 422, an adaptive equalizer 423, a data slicer 424, and an automatic modulation classifier 421, for demodulating a received analog signal. The microcontroller 413 is operably coupled to all the components, for example, 402, 403, 404,  $\ldots$ , 412,  $\ldots$ , 424 of the HART modem 400.

[0053] The sensor device 401a transmits an analog signal comprising a Highway Addressable Remote Transducer (HART) message to the HART modem 400. The analog-todigital converter (ADC) 402 of the HART modem 400 receives and converts the analog signal into digitized samples by sampling and digitizing the received analog signal at a sampling rate. The parallel-to-serial converter 403 converts the HART message in the digitized samples into serial data bit streams comprising binary information. The gray coder 404 divides each of the serial data bit streams into symbols and gray codes the symbols by performing a gray code lookup 404a in the predefined gray code lookup table 407 as disclosed in the detailed description of FIG. 6. The gray coded symbols are referred to as tribits. The microcontroller 413 executes computer program instructions defined by a tribit grouping module 405 for grouping a predetermined number of tribits and a predetermined number of the digitized samples to generate an index vector of the pregenerated sample lookup table 408 as disclosed in the detailed description of FIG. 8. The microcontroller 413 then executes computer program instructions defined by a phase modulated digital signal lookup module 406 for performing a phase modulated digital signal lookup in the pre-generated sample lookup table 408 to determine a phase modulated digital signal corresponding to the generated index vector, in the pre-generated sample lookup table 408. In an embodiment, the digital-to-analog converter (DAC) 410 of the HART modem 400 is a pulse width modulation (PWM) based DAC. The DAC 410 converts the phase modulated digital signal to a phase modulated analog signal and transmits the phase modulated analog signal to the sensor device **401***b* via the serial peripheral interface (SPI) **411**. The phase modulated analog signal is herein referred as a "HART coherent 8-ary phase shift keying (C8PSK) analog signal". The phase modulated digital signals in the pre-generated sample lookup table 408 are generated by the coherent phase shift keying modulator 412 and the microcontroller 413 as disclosed in the detailed description of FIG. 5.

[0054] The coherent phase shift keying demodulator 414 of the Highway Addressable Remote Transducer (HART) modem 400 receives an analog signal, that is, a HART coherent 8-ary phase shift keying (C8PSK) analog signal, from the sensor device 401b. The band pass filter 415 band limits the received analog signal to filter out different frequency components in the received analog signal before mixing the received analog signal with a carrier signal. The analog-to-digital converter (ADC) 416 converts the band limited analog signal into digitized samples. In the module 417, the high pass filter is operably coupled to the energy detector and the energy detector is operably coupled to the automatic gain control circuit. The high pass filter filters low frequency interfering signals from the digitized samples. The microcontroller 413 of the HART modem 400 compares signal amplitudes of the digitized samples with predetermined threshold values using the energy detector and determines further signal processing of the digitized samples.

[0055] If further processing of the digitized samples is required, the mixers 418 and the root raised cosine filters

419 of the coherent phase shift keying demodulator 414 generate an in-phase signal and a quadrature phase signal corresponding to each of the digitized samples. The decision estimator 422 performs a coarse estimation and a fine estimation of a phase error of each of the digitized samples for determining a resultant final phase error correction as disclosed in the detailed description of FIGS. 16-18. The decision estimator 422 further estimates a timing offset in each of the subsequent digitized samples using the coordinate rotation digital computer (CORDIC) 420 as disclosed in the detailed description of FIG. 19. The decision estimator 422 determines coefficients of the adaptive equalizer 423. The adaptive equalizer 423 minimizes noise and intersymbol interference in the subsequent digitized samples and generates demodulated digitized samples. The data slicer 424 assembles a character for character generation of the demodulated digitized samples and transmits the Highway Addressable Remote Transducer (HART) message as digital data as disclosed in the detailed description of FIG. 13. The automatic modulation classifier 421 validates presence of the received analog signal in the coherent 8-ary phase shift keying (C8PSK) protocol and absence of the received analog signal in the frequency shift keying (FSK) protocol, that is, the HART FSK signal at the input of the coherent phase shift keying demodulator 414 by determining signs of an in-phase signal and a quadrature phase signal corresponding to each of the subsequent digitized samples after performing the fine estimation of the phase error of each of the digitized samples and the estimation of the timing offset in each of the subsequent digitized samples. The automatic modulation classifier 421 detects an alignment of the in-phase signals of the subsequent digitized samples. If the automatic modulation classifier 421 detects a misalignment of the in-phase signals of the subsequent digitized samples, the automatic modulation classifier 421 asserts that the received analog signal is not in the C8PSK protocol and therefore, the received analog signal is in the FSK protocol. If the HART FSK signal is present, the HART modem 400 demodulates the HART FSK signal using a FSK demodulation method implemented by an FSK demodulator.

[0056] FIG. 5 illustrates a method for modulating and transmitting an analog signal comprising a Highway Addressable Remote Transducer (HART) message. The HART modem 400 comprising the analog-to-digital converters (ADCs), for example, 402, the parallel-to-serial converter 403, the gray coder 404, the coherent phase shift keying modulator 412 with the root raised cosine filters 412a and the mixers **412***b*, the digital-to-analog converter (DAC) 410, the microcontroller 413, the serial peripheral interface (SPI) 411, and the non-transitory computer readable storage medium such as the memory unit 409 exemplarily illustrated in FIG. 4, is provided 501. The HART modem 400 transmits the analog signal after modulation at a baud rate of 3200, that is, at 3200 symbols per second. Furthermore, the HART modem 400 uses a carrier signal of frequency equal to 3200 Hz to modulate the analog signal. The HART modem 400 receives the analog signal and modulates and transmits the received analog signal to a sensor device 401b exemplarily illustrated in FIG. 4, as a phase modulated analog signal.

[0057] The analog-to-digital converter (ADC) 402 of the Highway Addressable Remote Transducer (HART) modem 400 receives and converts 502 the analog signal comprising the HART message into a digital format or into digitized samples by sampling and digitizing the received analog

signal at a sampling rate. The parallel-to-serial converter 403 of the HART modem 400 converts 503 the HART message in the digitized samples into serial data bit streams. The serial data bit streams comprise binary information. The gray coder 404 of the HART modem 400 divides 504 each of the serial data bit streams into symbols and gray codes 504 the symbols using the predefined gray code lookup table **407** exemplarily illustrated in FIG. **6**. Each of the symbols comprises a predetermined number of consecutive bits in each of the serial data bit streams and represents a predetermined number of the digitized samples. For 8-ary phase shift keying, the symbols comprise three consecutive bits. The three consecutive bits are together referred to as a tribit. The left hand bit of the tribit corresponds to the first bit occurring in the serial data bit stream as the serial data bit stream enters the gray coder 404. The predetermined number of the digitized samples per symbol is 8. The gray coded symbols are encoded symbols where the adjacent symbols differ by 1 bit. According to C8PSK physical layer specifications of the HART protocol published by the HART Communication Foundation (HCF), the symbols are mapped into 8 phase angles as exemplarily illustrated in FIG. 6. The mapped phase angles have corresponding real parts and imaginary parts that are referred to as in-phase components and quadrature phase components of the symbols. In C8PSK modulation, the digital data, that is, the symbols are converted into 8 different sine waves having 8 different phases.

[0058] The microcontroller 413 and the coherent phase shift keying modulator 412 of the Highway Addressable Remote Transducer (HART) modem 400 generate phase modulated digital signals and store the phase modulated digital signals in the pre-generated sample lookup table 408 exemplarily illustrated in FIG. 4. The microcontroller 413 determines in-phase components and quadrature phase components of pre-gray coded symbols corresponding to analog signals received by the HART modem 400 by mapping the pre-gray coded symbols to predetermined phase angles in the predefined gray code lookup table 407. As used herein, "pre-gray coded symbols" refer to gray coded symbols corresponding to the analog signals with HART messages that the HART modem 400 has the capability to receive, modulate, and transmit. The predefined gray code lookup table 407 comprises gray coded symbols, the corresponding tribits, and the phase angles corresponding to the gray coded symbols as exemplarily illustrated in FIG. 6. The microcontroller 413 maps the pre-gray coded symbols to the phase angles in the predefined gray code lookup table 407 and determines the in-phase component and the quadrature phase component of each of the pre-gray coded symbols. The root raised cosine filters 412a of the coherent phase shift keying modulator 412 pulse shape the determined in-phase components and the determined quadrature phase components of the pre-gray coded symbols corresponding to the received analog signals. The mixers 412b of the coherent phase shift keying modulator 412 modulate the pulse shaped in-phase components and the pulse shaped quadrature phase components with a carrier signal for generating the phase modulated digital signals ahead of time as disclosed in the detailed description of FIG. 10. The microcontroller 413 stores the generated phase modulated digital signals in the pre-generated sample lookup table 408.

[0059] The microcontroller 413 generates 505 an index vector of the pre-generated sample lookup table 408 for indexing a phase modulated digital signal in the pre-gener-

ated sample lookup table 408 by grouping a predetermined number of the gray coded symbols and the predetermined number of the digitized samples. The predetermined number of the digitized samples is 8 to aid the root raised cosine filters 412a in pulse shaping the digitized samples. The pre-generated sample lookup table 408 comprises the phase modulated digital signals corresponding to index vectors generated by the microcontroller 413 as exemplarily illustrated in FIG. 11. The microcontroller 413 groups 3 gray coded symbols and 8 digitized samples and generates the index vector as exemplarily illustrated in FIG. 8.

[0060] The microcontroller 413 determines 506 a phase modulated digital signal in the pre-generated sample lookup table 408, corresponding to the generated index vector of the pre-generated sample lookup table 408. The pre-generated sample lookup table 408 is generated by the microcontroller 413 using the pre-gray coded symbols based on the frequency of the carrier signal being in synchronization with the baud rate of the phase modulated analog signal to be transmitted to the sensor device 401b by the Highway Addressable Remote Transducer (HART) modem 400. That is, the carrier frequency is equal to the baud rate of the HART modem 400. The index vector of the pre-generated sample lookup table 408 comprises 3n bits representing n gray coded symbols and m bits representing an index of the predetermined number of the digitized samples in each of the gray coded symbols. The values of n and m in the index vector of the pre-generated sample lookup table 408 are 3 resulting in the index vector of 12 bits indexing a phase modulated digital signal in the pre-generated sample lookup table 408. The size of the pre-generated sample lookup table 408 is base 2 raised to an exponent of 12, that is, 2<sup>12</sup>=4096 bytes. With the pre-generated sample lookup table 408 stored in the memory unit 409 of the HART modem 400, the HART modem 400 reduces power intensive computations in phase modulation of the received analog signal performed by the coherent phase shift keying modulator 412 in real time as the pre-generated sample lookup table 408 is generated ahead of time.

[0061] The digital-to-analog converter (DAC) 410 transmits 507 the phase modulated analog signal comprising the Highway Addressable Remote Transducer (HART) message, converted from the determined phase modulated digital signal, to the sensor devices 401b via the serial peripheral interface (SPI) 411. In an embodiment, if more precision is required, a pulse width modulation (PWM) based DAC 410 is used for converting the determined phase modulated digital signal to a phase modulated analog signal for further transmission. A sample rate of the transmitted phase modulated analog signal is 25600 hertz (Hz). That is, the HART modem 400 transmits the phase modulated analog signal at a sample rate=baud rate\*number of samples per baud=3200\*8=25600 Hz. In an embodiment, the sample rate of the transmitted phase modulated analog signal is 12800 Hz.

[0062] FIG. 6 exemplarily illustrates the predefined gray code lookup table 407 of the Highway Addressable Remote Transducer (HART) modem 400 exemplarily illustrated in FIG. 4. Coherent 8-ary phase shift keying (C8PSK) in the HART modem 400 comprises converting a serial data bit stream obtained from the digitized samples into 8 different sine waves having different phase angles. The 8 phase angles have a difference of 45° between them. The predefined gray code lookup table 407 comprises symbols formed by the

gray coder 404 by dividing the serial data bit stream and the 8 phase angles corresponding to the symbols. The gray coder 404 gray codes the symbols to generate gray coded symbols. The gray coded symbols have corresponding 8 phase angles. Each of the 8 phase angles corresponds to an in-phase component and a quadrature phase component of a gray coded symbol. The in-phase component of the gray coded symbol corresponds to a cosine component of the corresponding phase angle, and the quadrature phase component of the gray coded symbol corresponds to a sine component of the corresponding phase angle. Consider an example where a symbol 3 comprising three consecutive bits from the most significant bit (MSB) as 0, 1, 1 is received by the gray coder 404 of the HART modem 400. The gray coder 404 gray codes the symbol 3 and generates a gray coded symbol 2 comprising three consecutive bits from the MSB as 0, 1, 0. As exemplarily illustrated in FIG. 6, the phase angle corresponding to the gray coded symbol 2 in the predefined gray code lookup table 407 is -67.5°. The microcontroller 413 of the HART modem 400 exemplarily illustrated in FIG. 4, determines an in-phase component and a quadrature phase component of the gray coded symbol 2 as cos (-67.5°) and sin (-67.5°) respectively.

[0063] FIG. 7 exemplarily illustrates a constellation diagram 701 corresponding to the predefined gray code lookup table 407 shown in FIG. 6. The constellation diagram 701 is a two-dimensional XY-plane scatter diagram in a complex plane of the gray coded symbols. The gray coded symbols are represented by dots as complex numbers in the complex plane. As exemplarily illustrated in FIG. 7, the X-axis is a real axis and the Y-axis is an imaginary axis of the complex plane. In the complex plane, herein referred to as an "I/Q plane", the real axis is referred to as an in-phase axis (I-axis) and the imaginary axis is referred to as a quadrature phase axis (Q-axis). The 8 gray coded symbols and the phase angles are represented in the constellation diagram 701 as exemplarily illustrated in FIG. 7. The distance between the representation of the gray coded symbol and the origin in the I/Q plane defines the amplitude of the received analog signal corresponding to the gray coded symbol, and the angle between the representation of the gray coded symbol and the I-axis in the I/Q plane defines the phase angle corresponding to the gray coded symbol. Therefore, the in-phase component of the gray coded symbol is defined by the cosine component of the phase angle and the quadrature phase component of the gray coded symbol is defined by the sine component of the phase angle as disclosed in the detailed description of FIG. 6. The I/Q plane is divided into four quadrants. The gray coded symbols in the first quadrant have positive signs for both their in-phase components and their quadrature phase components. The gray coded symbols in the second quadrant have a negative sign for their in-phase components and a positive sign for their quadrature phase components. The gray coded symbols in the third quadrant have negative signs for both their in-phase components and their quadrature phase components. The gray coded symbols in the fourth quadrant have a positive sign for their in-phase components and a negative sign for their quadrature phase components. Consider an example where a gray coded symbol 5 comprising 1, 0, 1 as three bits with a phase angle of +157.5°. As exemplarily illustrated in FIG. 7, the gray coded symbol 5 lies the second quadrant of the I/Q plane and has a negative sign for its in-phase component and a positive sign for its quadrature phase component.

[0064] FIG. 8 exemplarily illustrates an index vector 801 of the pre-generated sample lookup table 408 generated by the microcontroller 413 of the Highway Addressable Remote Transducer (HART) modem 400 exemplarily illustrated in FIG. 4. The microcontroller 413 groups a predetermined number of the gray coded symbols, that is, 3 gray coded symbols, and a predetermined number of the digitized samples, that is, 8 digitized samples of a received analog signal to form the index vector 801. The size of the index vector 801 is 12 bits with 9 bits representing the 3 gray coded symbols and 3 bits representing the 8 digitized samples as exemplarily illustrated in FIG. 8. The index vector 801 is used for indexing a phase modulated digital signal in the pre-generated sample lookup table 408. The bits of the first gray coded symbol, symbol 0, are in positions 9, 10, and 11 of the index vector 801, the bits of the second gray coded symbol, symbol 1, are in positions 6, 7, and 8 of the index vector 801, and the bits of the third gray coded symbol, symbol 2, are in positions 3, 4, and 5 of the index vector 801. The bits in the positions 0, 1, and 2 of the index vector 801 indicate an index of the 8 digitized samples per gray coded symbol corresponding to which a phase modulated digital signal is generated and stored in the pregenerated sample lookup table 408. The index of the 8 digitized samples per gray coded symbol starts from 0 and increments up to 7.

[0065] Each of the 8 gray coded symbols can be represented by three consecutive bits and each gray coded symbol has 8 digitized samples. Thus, the index vector 801 of 12 bits can index 8\*8\*8\*8=4096 digitized samples in 512 phase modulated digital signals in the pre-generated sample lookup table 408. That is, the index vector 801 can index 512 different coherent 8-ary phase shift keying (C8PSK) modulated waveforms, that is, the phase modulated digital signals with 8 digitized samples each. The index vector 801 points to a position in the pre-generated sample lookup table 408 where the phase modulated digital signal corresponding to a combination of the 3 gray coded symbols and the 3 bits representing an index of the 8 digitized samples is located. The pre-generated sample lookup table 408 comprises the 512 C8PSK modulated waveforms with the 8 digitized samples each. Prior to generation of the index vector 801, the phase modulated digital signals, that is, the different C8PSK modulated waveforms are assembled in the pregenerated sample lookup table 408 by the microcontroller 413 and the coherent phase shift keying modulator 412 exemplarily illustrated in FIG. 4. With the pre-generated sample lookup table 408, the C8PSK modulated output, that is, the phase modulated digital signals are determined with a substantially less number of instructions.

[0066] FIGS. 9A-9C exemplarily illustrate impulse responses of one of the root raised cosine filters 412a of the coherent phase shift keying modulator 412 of the Highway Addressable Remote Transducer (HART) modem 400 exemplarily illustrated in FIG. 4. Each of the root raised cosine filters 412a pulse shapes an in-phase component and a quadrature phase component of each of the pre-gray coded symbols. The impulse response of one of the root raised cosine filters 412a is the output of that root raised cosine filter when presented with an impulse as an input. The root raised cosine filters 412a are assumed to be 2 bauds or symbols and 1 sample long. Thus, the root raised cosine filters 412a are 3 bauds in filter length, that is, the root raised cosine filters 412a have 17 taps and operate at a sample rate

of 25600 Hz. In the impulse response exemplarily illustrated in FIGS. 9A-9C, the Y-axis represents output of one of the root raised cosine filters 412a for pulse shaping, for example, the in-phase component of each of the pre-gray coded symbols and the X-axis represents the 8 digitized samples per pre-gray coded symbol. Each number on the X-axis indicates a position or an index of a digitized sample in the pre-gray coded symbol whose in-phase component or quadrature phase component is input to one of the root raised cosine filters 412a. When moving from one digitized sample to the next digitized sample of the baud or the pre-gray coded symbol in one of the root raised cosine filters 412a, the I/Q waveform, that is, the impulse response shifts to the next index of the digitized sample in the pre-gray coded symbol. The impulse response shifts from a position exemplarily illustrated in FIG. 9A, to a position exemplarily illustrated in FIG. 9B, as a second digitized sample in the pre-gray coded symbol N-1 is being modulated. Similarly, the impulse response shifts from the position exemplarily illustrated in FIG. 9B, to a position exemplarily illustrated in FIG. 9C, as a third digitized sample in the pre-gray coded symbol N-1 is being modulated. After the eighth digitized sample in the pre-gray coded symbol N-1 is modulated, the digitized samples in the pre-gray coded symbol N-2 move to the next digitized sample positions in the pre-gray coded symbol N-1. The root raised cosine filters 412a generate a pulse shaped in-phase component and a pulse shaped quadrature phase component for each of the 8 digitized samples of a pre-gray coded symbol. The mixers 412b of the coherent phase shift keying modulator 412 exemplarily illustrated in FIG. 4, generate an in-phase (I) signal and a quadrature phase (Q) signal by mixing the pulse shaped in-phase component and the pulse shaped quadrature phase component with a cosine component and a sine component of the carrier signal respectively, for each of the 8 digitized samples of the pre-gray coded symbol. To obtain the pulse shaped in-phase component and the pulse shaped quadrature phase component for each of the 8 digitized samples per pre-gray coded symbol, the impulse responses of the root raised cosine filters 412a are slid over the 8 digitized samples per pre-gray coded symbol as exemplarily illustrated in FIGS. 9A-9C.

[0067] FIG. 10 exemplarily illustrates a flow chart comprising the steps performed by the microcontroller 413 and the coherent phase shift keying modulator 412 of the Highway Addressable Remote Transducer (HART) modem 400 exemplarily illustrated in FIG. 4, for generating a pregenerated sample lookup table 408 exemplarily illustrated in FIG. 4 and FIG. 11. The pre-generated sample lookup table 408 is generated in non-real time for use in real time by the microcontroller 413. The pre-generated sample lookup table 408 in real time replaces the coherent phase shift keying modulator 412. The microcontroller 413 accesses 1001 the predefined gray code lookup table 407 and maps pre-gray coded symbols to predetermined phase angles in the predefined gray code lookup table 407. For the pre-gray coded symbols and the 8 digitized samples per pre-gray coded symbol, the root raised cosine filters 412a of the coherent phase shift keying modulator 412 exemplarily illustrated in FIG. 4, determine the impulse responses as exemplarily illustrated in FIGS. 9A-9C. With 17 taps, the root raised cosine filters 412a span 3 bauds or symbols of the received analog signal. The carrier frequency being in synchronization with the baud rate of the analog signal, that is, the HART coherent 8-ary phase shift keying (C8PSK) analog signal to be transmitted by the HART modem 400, allows the microcontroller 413 to calculate the outputs of the root raised cosine filters 412a for the determined in-phase component and the determined quadrature phase component for each of the digitized samples in each baud corresponding to the predetermined phase angle in the predefined gray code lookup table 407. The sum of the output of the root raised cosine filters 412a of the 3 bauds, that is, the pre-gray coded symbols N-2, N-1, and N is calculated and then multiplied with a carrier signal in the coherent phase shift keying modulator 412. The output of the root raised cosine filters 412a is a product and a summation of the determined in-phase components and the determined quadrature phase components of the pre-gray coded symbols x[k-i] and the filter coefficients a, given by the expression below:

$$Y[k]=\Sigma^{17}_{i=0}a_{i}x[k-i]$$

[0068] The filter coefficients a, are derived from the impulse responses of the root raised cosine filters 412a. The microcontroller 413 points 1002 to a first digitized sample of a first pre-gray coded symbol N. The output of the root raised cosine filters 412a at the first digitized sample of the first pre-gray coded symbol N is a product of an in-phase component and a quadrature phase component at the first digitized sample of the pre-gray coded symbol N and impulse responses of the root raised cosine filters 412a at the first digitized sample of the pre-gray coded symbol N. The microcontroller 413 computes 1003 a sum of the output of the root raised cosine filters **412***a* at the first digitized sample of the first pre-gray coded symbol N. The output of the root raised cosine filters 412a involves all 8 digitized samples of the pre-gray coded symbol N-2, all 8 digitized samples of the pre-gray coded symbol N-1, and the first digitized sample of the gray coded symbol N. For the second digitized sample of the pre-gray coded symbol N, the impulse response is shifted to the right by 1 position as exemplarily illustrated in FIG. 9B. Then, the output of the root raised cosine filters 412a involves 7 digitized samples of the pre-gray coded symbol N-2, all 8 digitized samples of the pre-gray coded symbol N-1, and the second digitized sample from the pre-gray coded symbol N. For the first digitized sample of the first pre-gray coded symbol N, the coherent phase shift keying modulator 412 multiplies 1005 the pulse shaped in-phase component and the pulse shaped quadrature phase component with a cosine component cos(w<sub>c</sub>t) and a sine component sin(w,t) of the carrier signal 1004 respectively. The coherent phase shift keying modulator 412 generates 1006 a phase modulated digital signal corresponding to the first digitized sample of the first pre-gray coded symbol N using the mixers 412b of the coherent phase shift keying modulator 412 exemplarily illustrated in FIG. 4.

[0069] The microcontroller 413 and the coherent phase shift keying modulator 412 repeat 1007 the steps 1002 to 1006 for all the 8 digitized samples of the pre-gray coded symbol N. The microcontroller 413 and the coherent phase shift keying modulator 412 repeat 1008 the step 1007 for all combinations of the pre-gray coded symbols and the digitized samples per pre-gray coded symbols and the digitized samples per pre-gray coded symbol corresponding to analog signals received by the Highway Addressable Remote Transducer (HART) modem 400, resulting in a pre-generated sample lookup table 408 with phase modulated digital signals. The microcontroller 413 of the HART modem 400 uses fewer additions and subtractions in gen-

erating the pre-generated sample lookup table 408 and minimizes the number of additions and multiplications performed in real time. The operations of additions and subtractions are performed in the raised cosine filters 412a and the mixers 412b in the coherent phase shift keying modulator 412. The size of the pre-generated sample lookup table **408** is 8\*8\*8=512\*8=4096 bytes. The pre-generated sample lookup table 408 has 4096 table values, that is, 512 phase modulated digital signals with 8 digitized samples each. The microcontroller 413 pre-calculates these different phase modulated digital signals and stores the phase modulated digital signals in the memory unit 409 of the HART modem 400 exemplarily illustrated in FIG. 4, in the form of the pre-generated sample lookup table 408. In an embodiment, the HART modem 400 stores the pre-generated sample lookup table 408 in a non-volatile memory of the microcontroller 413. In an embodiment, the pre-generated sample lookup table 408 is generated by a secondary microcontroller apart from the microcontroller 413 of the HART modem 400.

[0070] The Highway Addressable Remote Transducer (HART) modem 400 generates the pre-generated sample lookup table 408 since the frequency of the carrier signal is equal to the baud rate of the phase modulated analog signal. Thus, the carrier signal is in exact phase at the end of each pre-gray coded symbol. The number of computing cycles required by the coherent phase shift keying modulator 412 is substantially lowered by using the pre-generated sample lookup table 408. In an embodiment, using a microcontroller MSP430 of Texas Instruments Inc., the pre-generated sample lookup table 408 is generated in less than 1 megahertz (MHz) of computing cycles. Due to the less number of computing cycles, significant power and cost savings are achieved in the HART modem 400.