US008732538B2

# (12) United States Patent

# Krishnamoorthy

# (10) Patent No.: US 8,732,538 B2 (45) Date of Patent: May 20, 2014

# (54) PROGRAMMABLE DATA STORAGE MANAGEMENT

(75) Inventor: Senthil Kumar Krishnamoorthy,

Sunnyvale, CA (US)

(73) Assignee: **ICForm, Inc.**, Sunnyvale, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this

patent is extended or adjusted under 35

U.S.C. 154(b) by 280 days.

(21) Appl. No.: 13/416,027

(22) Filed: Mar. 9, 2012

(65) **Prior Publication Data**

US 2012/0233523 A1 Sep. 13, 2012

#### Related U.S. Application Data

- (60) Provisional application No. 61/451,139, filed on Mar. 10, 2011.

- (51) Int. Cl. *G11C 29/00* (2006.01) *G06F 11/10* (2006.01)

- (52) **U.S. CI.** CPC ...... *G06F 11/1072* (2013.01); *G11C 2207/102* (2013.01)

CPC ...... G11C 2207/102; G06F 11/1072

USPC ...... 714/722, 718; 365/201

See application file for complete search history.

(58) Field of Classification Search

# (56) References Cited

### U.S. PATENT DOCUMENTS

| 6,041,001 | A *  | 3/2000  | Estakhri        | 365/200 |

|-----------|------|---------|-----------------|---------|

| 7,013,378 | B2 * | 3/2006  | Motta et al     | 711/203 |

| 7.120.729 | B2   | 10/2006 | Gonzalez et al. |         |

| 7,170,788 | B1   | 1/2007 | Wan et al.              |  |  |  |  |

|-----------|------|--------|-------------------------|--|--|--|--|

| 7,218,552 | B1 * | 5/2007 | Wan et al 365/185.18    |  |  |  |  |

| 7,355,888 | B2   | 4/2008 | Hemink et al.           |  |  |  |  |

| 7,355,889 | B2   | 4/2008 | Hemink et al.           |  |  |  |  |

| 7,539,920 | B2   | 5/2009 | Choi et al.             |  |  |  |  |

| 7,660,941 | B2   | 2/2010 | Lee et al.              |  |  |  |  |

| 7,716,415 | B2 * | 5/2010 | Sharon 711/103          |  |  |  |  |

| 7,734,861 | B2   | 6/2010 | Li et al.               |  |  |  |  |

| 8,174,905 | B2 * | 5/2012 | Shalvi et al 365/185.29 |  |  |  |  |

| (C + 1)   |      |        |                         |  |  |  |  |

#### (Continued)

#### OTHER PUBLICATIONS

Jim Chen; Har, D.; Mak, K.; Schulz, C.; Tremaine, B.; Wazlowski, M., "Reliability-availability-serviceability characteristics of a compressed-memory system," Dependable Systems and Networks, 2000. DSN 2000. Proceedings International Conference on , vol., No., pp. 163,168, 2000.\*

#### (Continued)

Primary Examiner — Steve Nguyen (74) Attorney, Agent, or Firm — Ash Tankha; Lipton, Weinberger & Husick

## (57) ABSTRACT

A method and system for managing storage of one or more data blocks in a programmable data storage device is provided. A data storage controller partitions each of multiple data blocks into multiple sub data blocks comprising a number of bits based on one or more index value descriptors. The data storage controller generates transition vectors from each of the sub data blocks by applying one or more transition functions. The data storage controller encodes one of the transition vectors for each sub data block for obtaining a residual sub data block comprising a reduced number of bits, thereby resulting in increased bit space. The data storage controller generates a composite data block by merging each residual sub data block. The composite data block is configurable for writing to one or more regions in the programmable data storage device free from a disturbance caused by write operations to other regions.

#### 36 Claims, 13 Drawing Sheets

## (56) References Cited

# OTHER PUBLICATIONS

## U.S. PATENT DOCUMENTS

| 8,458,568    | B2 * | 6/2013  | Cideciyan et al   | 714/774 |

|--------------|------|---------|-------------------|---------|

| 8,533,564    | B2 * | 9/2013  | Yurzola et al     | 714/763 |

| 2010/0042900 | A1*  | 2/2010  | Khmelnitsky et al | 714/764 |

| 2010/0157675 | A1   | 6/2010  | Shalvi et al.     |         |

| 2011/0066922 | A1*  | 3/2011  | Wezelenburg et al | 714/773 |

| 2011/0320915 | A1*  | 12/2011 | Khan              | 714/773 |

Ningde Xie; Guiqiang Dong; Tong Zhang, "Applying transparent lossless data compression to improve the feasibility of using advanced error correction codes in solid-state drives," Signal Processing Systems (SIPS), 2010 IEEE Workshop on , vol., No., pp. 31,35, Oct. 6-8, 2010.\*

<sup>\*</sup> cited by examiner

FIG. 1

FIG. 2A

FIG. 2B

**FIG. 3**

**FIG. 5**

May 20, 2014

FIG. 8

6AA4C87EE71234C4FBBB3F7718954A38DDAF53BCEDFAF22EB42DD265FAB89F7F1E1E9F1B4A50FB776E08DE4342FE5B86FBB72E08604052519F007A41 7D2B399915EE35E650DA53FD93563C8EFE27EEE533FE37996ECF4153469C650002060AB52E9FE9C196DEDB0008C28CAF2EB6A48CCD828597F5069B6AC 70692923E2A7F5C774462B3F15A72D9504209224D5CD6A1C08FC145C7121344F908E49C2C7F6A7848ABB26708E7EEA90F54435EBE05DC837DC82D1841E9AC3015AE00ED132F23E871B1B2B59A9A0FA8931C8EBB7EBD1D7B94CDD255921EAC21E17042FA3E48A21DA064927A3F693464FAB5FF023A413E21D1 800A85A66490AB3B9F9CDD00872CCC030916D9019379EAE4B48129F1B49E0DD89AFA2DECA1A59CF4C0E4790F99922D28520D2032BBAB7D81E09031404 33BF8839975D8D7BEFD62A3958104C5DFD2C11A266E4E40244D8BA4965AC0EC0F4B6D789A8CB797D3C08540F1F2F797DA42031EDDC3697D5743A5542 CD8578C160AF0CD3AEEACA4CE34131F49FA1C449EFA8FE0A81BAB43136B281E62F9A003CCDF17EBDA6C957587FF8E90ACADF19E0CC1BAA2EF2A5 A14713854D9E39DB36DC148EC81F2A3DC2BD8C27F447CE58911D7AE41A6D8E090FB86AFE0CB841E595666979BEBF22D9EFD96C6FED7EF3FE12F4C0C JF4814D79BA9086C3HD2C00BC078BF3A2952119DEA4493A6CDCCC58FA2979A9E13FD483555EBA627E2B3CBCD466560D0DB7C72C67315A6A70A733E \$F9A682906574663ABC5242D9AE0A52D75DE5A3BD33A4AEDBCCC57B77293852D9884BB0EA562BFABE4A13EBC23C50BFAF948494373EBB4885C319A 0CA72AA7CCA1535D0389B0E03E4D1FAA99989755E13DC2184F784C88C8405A3BAD52C76DAE493FCA4CA63DF2AFA17F9FE2FA900BD7FCBAAE6C9B 11AE681CE22CB02A58BFB5FF2D9C41AD791AD49D7A1F498DFDBE80942968CE9CFC3AC588796A6466D6592FD619762829432E08F723A2B506AE7DEB 8ECD A4354B9D9815216A6329099C0B5C57A6B2C0EC44DE405C2D74FB55EE78B5D3175AE49DDB932B6E81302BCF550B8544681F06BDEA142A5D5A93C 0CE25FBE0800B3E34E26AF7A02296CE987FA516182E00E96400D75F9B5D4DC7B02C71016786ECEC3C6803A87933EF7C723903DE99221240350191770C10 D474E99BE4BC20BAF4FAEFCDDA5A0E7DE51F42D9DFCB4AB932C6F94B6F8C6D2FE18E177FF54F0189B6101B741D54484F04AF7C2F9E2C3A776CAC85 58F3FC9AA63DE95EDF1440A7385A5890A22CF5C4B459139E00685739E6A36DCBD2846303C89A8CF9EEFB750E4CF34995041DA4B820948BC41C4F76305 9F6A5A5AD84F74B54426E7A2C68E4A64FDB5B1CBE2A74624FC46B72EEE5C85DB9A530D034DBF29BFDA1AA3953071A8EABCA5F25B071F3B7A0FB31

3495A0D4A4749142CT8DB7B26C0C2AD984920TCD0D22C9188BG709E0A5663DC2E12E5C11205FC7E2515863388CAA06260F2AF89EC0BD1F0808FA2233

CED758936236C18F800970537A7EC6A1EEA0C4B690303F7A832E4C8CF3FC4F442A360C82021D47F8EE707D21381DF48ED9BBB64207652F1432C37AA50B 8637B7B2AF5AD8A8F6DE210306C46ADC619F563E4B5CC58E910D793158DF3836FC0EBD5A9B2A7D1A7673CE1BA9B2B4CE26200C816D9951C1198B8C6 6DE3077D13C5DD124D42CAD1D941B2E7598ADE967251638626F3C0E17E6F853FB1E7CD1348A0BFCB8FC03D3F7A022487729A59399E886A178D73B59E1 OOADF7BF61829A98496CEBF1ADEE615C902839A7760A4E086E743BB426198B69E8D60C18061D708986ECAB09E2A7827A0DFE1462F02E53687B43C7E5B CE6A4418F812984682422FEF4158D885793A2C512092878ED638451A68D2B0A04DBF6D8F8AA762222FF6F4F5B10366989B492F39DE17C2A061C29C498EB 8BF904171EB3E050CDC830245F089C7B8B3EEDF15807DF7A71EC4C29AEE48CFF8DC50112A92AC00B0BEEF469E3269B1B0A097971457A2DAA9BF935A E988837A909A7F2F655F98C9035FDD859164480560B92FC22FC960CB929B04F6A471986130678EB5F716D9C0EE96267F14BD2C30AD9DEB8C0C19C7EF45 06A0018BC9E55E97A4E44D4C99E29701F05D35FE4003AA88598600CA04561DF1158A619CAC4214B7E9601EAC1233EB4464728715E28AD34027BBE3F351 621D818E9CD4A92B338DEB99743B192D78D87C6E098A4956F8A526832154B655F41B1FD81F104B4489D3EC62E87171B5DA2CACC11B6196ED144917C65 CCD8D3019C6D4EFC8D4208A07C24B469C5202361043825CD7258A459DC9D92A078B693CDD81FCA447B49A291300AFE3CE9050E722A4555062EA5079A 784D718E11F47C065586802EECE26CEFAB39654303BA240307906D3A2873B4A529388290554E283BA055C660592F823403D3CCF3E018C2ABD9E04411B04 216D2709C7FACF7643CAD0491AC256E00D35027843FE6BE14B85A97D3E449AA3AE0BC6C85F1187D70E978381D23EDA4BDBCB225AB972AC904449933 E6B8220F634E94B3F7756DCEB926B3072F463B3F5DB97C2ED66A19574025E763228B7349CE89283638FB6C763C426DFBC6B77A6DA723596411721E05797 3B20695E1985A7212F83929FB9BE63FDC92B3EB5BB4748C4A54D0701F5C679817F08390A9B1ADD86B682ABC5282CD8DE7CA454A203C5CFA2EF39F5B )3D6B4F219D66053EB223028D40137EED94A6731FAF2C6D83A205750BFDA1544F829EFF560598DED72D2D854EB70D1D5263E77475C5055872C500D

/IECEBF6604F50A70F722DD31D9BC2D4A3C06FB4E75722F29237491223C456081483C2CCF5918E89875B4B25B0C1A1A7C3828B666C67140BC8D3CC99905

ECBE092F54C20DB80F5B88F839D2F61F0084923111B5047FD16B4B43F1FA548D28DDF0C5F81377D71E1CC0730C6C60F03E314BE8CD4E8FE5FCF2 CF140E02B55DD04A4F4BD6CF01C6B1A9D31E64CC4F9F99517783C3C81C05E36D69D70FCB570920CD43AE0D0C3116C81D93AF5F289B0BE8AD908982A2C2B07F843D384D6665CE67983871C8A7D393575EAC30F32CF8C730F3285C40C5810CBEB57F2420C914C28D17DFEC3663D9E0FC54F1C0347 1307DD0139D754D9B9F82A7C4150075102E9C56BCFC01E760C9A2F8FDBA32D1AC312B11CFA84FD30C7B07060E9E036FAC2857134BC4731E711D 4373228000BF071A3FF931ECE23081EF3E33E4DD1C8425E003CEBCEC13336728F6DB671CC64133B0F30879E318636952AD0271F4644BBDC7EE135 CA314B2DF2CDDSF3365496870D60042FDB23443B6EF7447002373AD5031FF4770D3A07208FB09604E3FDD47C1711CD69039FC04E0D5F31CSB3490 F0F1DC301C2FC3D60C0A1B336D541DF4B813CF36C3C41D0305CDF342FB66218043F83C61C08BEC38FF0945047E67FF9CB00087DD360431FDF4B5 45167F5E8CA23B64E1F82A59BA5DC7FC724CE4CF35DC3AAC12E30983F4C3332B4BDFC8DDC161F17C4F15354A0E353C0CE41F4DE8DCBC4879D 850C57C386F7471498D05E32A450FFFE8C1B51C3C07E4DC0B8ED004E5F5F96C31393AD7B4B30F79FB506C57D9FCC5C4C46A201F84D0C93FCS460 208BF91113EB3A7009485F2B0C1112399FC87F436C0CED07D52E35C16D6747D224055F8E397223B715F15672DFC612437BF5395D021C43EF22834B9 IF2C81993DBC1C3CA8EC0D8C933F5FB0525CD0770A1DC72302D33C70053EF2D1B08D46934B5D67DBEC0DE5033D192B64F33E2A878239C3F8990 0C76EF1537CC72651F2D71F40E37C04C41733F79A60D205F4D7DC7891D7D4F100A16FF3EC013FF44FCB6A7C53EBC8F5E033D323C5EE3DD983381 29EDC8078DE19C0EF0FF267EC1C4F465EF336C27C0FB6C027F7E5664FFCF4608C94F708CDF5CC86BCC158A031577F228D7DCC1338F4D63530D48 0747B48CC0FB90936B0C3DC760E3563C17E8CF53C6177F233F13431436EC745F7CE0B30F35D64370AFB3D0013D42ACA8B19D8CD57E0F6161FDA1 D633D097FB4E64012C3F905307C4459FB2D131B53CCFE402CF18108A5563CCF73FC0714037DAD5BC24E12D5F05C233E26615D133F39C807BD4CC 31F379C238444132FC3310F4B62B62C7E180FC43E36DB2F0C71EBB79E1081F109FD50E21B74F4330FDFDB8340GF58C00D36FB2B3F7B9783514328C0A7855C34C3B480DEC8F91C300BC8CF1B73762DF1040D4B1FE0E168744E443D1837C3E1CDF74EBBF617632F313DA0410D0802D22F0F53E78CC47 95C45D8F93C4531DDAFDB03ECCCD31CFF3DB00C328F05780CC7D4340D4C33E2080F81F43C47CF40DE3F372CF13F34102CF51CC1C0EE3F4351E CD0DED0F5EE4DF1790F75C1C583D3501F09F30A89397F27CD1316F8C3C0B5C2C2A4EC7FCC817D31D4447077770F27187350C25F1CDC63BBC849 4B63E432960FAF164EB136301 ACBD724362A01E4D24D3BFF41CC482DCF2ECD87D3C239C2780DB2CDB9DB00F9E5832EF70F45D0D0FD80FFCE4 600D391D0C01F763F95DEF790447C11F13E230250F5EB8C911634C077BD7C34078C1F42BB5F7102EFD829820F40F32DD451C53EBF81952C2DD38D 741FDD861A23338FC58778FF19F393379F407131E0C75783D8FCA7D9F02A043E0C9C3871F56D32B8CD8034CFC2D3C7D445F014CB5C30DAB7C30 F10275ECF378C733740CFFC8102584CBDF95F9107BF0D61E5FF1CE10B07F01D0DD803BE44F70B82F23B331C56320690F0E179C3AFDF4357BFD321 EFD1062DCDF34F296AA75642C967777C21E9CSD295C9D75C5C318F044B0CDCC10C3D4F3E395F71090A1C1777180C3B083E07ED7D0C11C6CC60

FIG. 1

May 20, 2014

FIG. 1

# PROGRAMMABLE DATA STORAGE MANAGEMENT

# CROSS REFERENCE TO RELATED APPLICATIONS

This application claims the benefit of provisional patent application No. 61/451,139 titled "Programmable Data Storage Management", filed on Mar. 10, 2011 in the United States Patent and Trademark Office.

The specification of the above referenced provisional patent application is incorporated herein by reference in its entirety.

#### **BACKGROUND**

The method and system disclosed herein, in general, relates to storing data on a flash memory device. More particularly, the method and system disclosed herein relates to controlling the number of cells programmed to store data in a 20 flash memory device and improving error recovery.

Flash memory devices use floating gates to store data. Flash memory devices comprise cells, for example, single level cells and multi-level cells. A single level cell (SLC) in a flash memory device holds one bit per cell. A multi-level cell 25 (MLC) on a flash memory device holds multiple bits in each cell, which reduces the cost of flash based storage. As fabrication process geometries on flash memory devices shrink and the cells get smaller, charge in the floating gates gets smaller, and the cells are more prone to errors. Moreover, the 30 endurance of each cell, that is, the number of times a cell can be programmed and erased, decreases with process geometries. Multi-level cell flash arrays are particularly susceptible to error due to shrinking geometries. Data retention in flash cells is also affected, for example, by read operations and 35 write operations on neighboring cells, also referred to as read disturb and program disturb respectively.

Using flash memory devices, for example, solid state drives (SSD) to store data and replacing rotating magnetic storage devices, for example, hard disks, is gaining rapid traction due 40 to the reduction in prices of multi-level cell flash memory devices. The data to be stored in the solid state drives requires mapping of logic storage blocks into flash blocks and pages. In most cases, logical addresses have more writes than others. Since the endurance of a page of a flash memory is limited, 45 data from pages that are not frequently used are moved to accommodate pages that are more frequently used. This mechanism for prolonging the service life of solid state drives referred to as "wear leveling" creates write amplification, that is, it increases the number of writes on multi-level cell flash 50 memory devices. Write amplification also occurs due to thresholds associated with read disturb, and from garbage collection to recover storage space from blocks of data that are deleted.

Numerous solutions have been proposed to increase the 55 endurance of flash cells. There are two broad categories of solutions to improve flash memory performance in SSD storage. The first category involves circuit techniques that improve the cells in flash memory devices and associated read/write circuits. In addition, circuit techniques have been proposed to limit the effect of disturb to neighboring cells during a write operation of a block of data. The second category involves signal processing steps that improve data recovery and reduce the effect of cell interactions. Several solutions for program disturb have been proposed which alter 65 the sequence of rows for block writes to flash memory devices. These solutions reformat the data to be stored to

2

match the characteristics of flash memory device cells and arrays. For example, one solution proposes reduction in program disturb by reducing the number of cells that are not programmed and altering the distribution of programmed values. Another solution avoids program disturb by randomizing the data to a flash memory resulting in fewer cells that are not programmed, and changes in the distribution of programmed values when the data remains the same. However, these solutions do not help in applications that need faster programming. These solutions often fail to limit the number of write operations to fewer flash cells. Moreover, these solutions often fail to reduce the number of erase operations on the flash cells by performing erase operations on fewer flash cells. Furthermore, a number of these solutions operate on the 15 original data block rather than reorganizing the data in the data block to enable faster programming. This raises a significant problem since with the probability of bit errors increasing with the shrinking of flash cell sizes, the number of bit fields required to accommodate error correction bits increases. Conventional solutions for improving flash memory performance often store the error correction bits in a separate page and region of the flash memory. However, these solutions are constrained by a predetermined number of bits set for error correction, thereby allowing correction of the same number of bit errors for all data, which does not allow the flexibility of changing the number of error correction bits in accordance with the data programmed in a page.

Hence, there is a long felt but unresolved need for a method and system that manages storage of one or more data blocks in a programmable data storage device by minimizing the number of cells that go through program erase cycles for each write, while minimizing the effect of program disturb. Moreover, there is a need for a method and a system that reduces the number of columns in the programmable data storage device that are to be written. Furthermore, there is a need for a method and system that improves the recovery of a number of bit errors. Furthermore, there is a need for a method and system that reconfigures the data programmed into a page for enabling a dynamic generation of a number of error correction bits for the page based on the reconfigured data, thereby allowing a flexible configuration of error correction bits and improved error correction.

#### SUMMARY OF THE INVENTION

This summary is provided to introduce a selection of concepts in a simplified form that are further disclosed in the detailed description of the invention. This summary is not intended to identify key or essential inventive concepts of the claimed subject matter, nor is it intended for determining the scope of the claimed subject matter.

The method and system disclosed herein addresses the above stated need for managing storage of one or more data blocks in a programmable data storage device by minimizing the number of cells that go through program erase cycles for each write, while minimizing the effect of program disturb. The reduced write width allows hiding of columns with bad cells, for example, by skipping bad columns. The reduction in the number of bits can be used to speed up writes, that is, by writing fewer columns in a sequence. The reduction in the number of written columns ensures that the usage of the columns can be recycled to improve future write operations and reduce the impact of write disturb, that is, writing fewer columns in any order.

Furthermore, the method and system disclosed herein addresses the above stated need for improving the recovery of a number of bit errors. The increased recovery of bit errors is

achieved by addition of more error correction bits, that is, error correcting code (ECC) bits to a composite data block. Furthermore, the method and system disclosed herein address the above stated need for reconfiguring the data programmed into a page for enabling a dynamic generation of ECC bits for 5 the page, based on the reconfigured data, thereby allowing a flexible configuration of the ECC bits and improved error correction. The number of ECC bits can be calculated dynamically based on the data. The method and system disclosed herein enables the transfer of bits in the columns 10 between different programmable data storage devices subsequent to processing of the data, which reduces the effort required in each subsequent copy or wear-leveling write operation. The method and system disclosed enables merging of two or more data blocks during a copy operation performed 15 between programmable data storage devices, thereby improving the transfer bandwidth, improving wear-leveling write operations for reducing write amplification in a programmable data storage device, etc.

The method and system for managing storage of one or 20 more data blocks in a programmable data storage device disclosed herein provides a data storage controller comprising at least one processor configured to control configuration of the data blocks for storage of the data blocks in the programmable data storage device. The data storage controller 25 partitions each of the data blocks comprising multiple bits into multiple sub data blocks based on one or more index value descriptors. As used herein, the term "index value descriptor" refers to a function that defines a sequence of numbers that determines the order of arrangement of bits 30 extracted from a data block for generating new bit streams for sub data blocks from the original bit stream of the data block. Each of the sub data blocks comprises a distinct sequence of a number of bits. Each of the sub data blocks is obtained by extracting bits corresponding to the index value descriptors 35 stored in a lookup table. In an embodiment, the data storage controller creates data redundancy by replicating the bits of each of the data blocks in one or more of the sub data blocks on partitioning the data blocks.

The data storage controller generates transition vectors 40 from each of the sub data blocks by applying one or more transition functions on each of the sub data blocks. The transition vectors constitute a transition set for each of the sub data blocks. As used herein, the term "transition vector" refers to a bit stream comprising bits in a sequence, with a low ratio 45 of one bits herein referred to as "ones" to zero bits herein referred to as "zeros" or a low ratio of zeros to ones, obtained from a bit stream of a sub data block by application of a transition function. One or more of these bit streams have a lowest possible ratio of ones to zeros or zeros to ones. Also, as 50 used herein, the term "transition function" refers to a reversible mathematical transformation that modifies the bit stream of the sub data block to obtain a bit stream with the desired ratio of ones to zeros or zeros to ones. The data storage controller performs one or more reversible mathematical 55 transformations on the distinct sequence of bits in each of the sub data blocks for generating the transition vectors.

In an embodiment, the data storage controller selects one of the transition vectors in the transition set based on selection criteria for encoding the selected transition vector. The selection criteria comprise, for example, one of a predetermined ratio of ones to zeros, a lowest number of ones or zeros, a total number of ones lesser than a predetermined threshold, etc. The data storage controller encodes the selected transition vector for each of the sub data blocks for obtaining a residual 65 sub data block comprising a reduced number of bits for each of the sub data blocks, resulting in increased bit space for

4

accommodating parity bits and error correction bits. As used herein, the term "bit space" refers to a number of vacant bit positions in a data block. Also, as used herein, the term "residual sub data block" refers to a sub data block obtained by replacing the original bit stream in the selected transition vector with the bit stream having the shortest encode length for the selected transition vector. The data storage controller replaces the bits of each of the transition vectors with the encoded bits from each of the transition vectors to obtain residual sub data blocks. The data storage controller, for example, performs run length encoding (RLE) on the selected transition vector for each of the sub data blocks for obtaining the residual sub data block comprising a reduced number of bits for each of the sub data blocks. In an embodiment, the data storage controller generates distinct index value descriptors for partitioning each of the sub data blocks for enabling an optimal performance of encoding of the selected transition vector for each of the sub data blocks.

The data storage controller generates a composite data block by merging the residual sub data block of each of the sub data blocks. As used herein, the term "composite data block" refers to a data block obtained by combining one or more residual sub data blocks. The composite data block comprises increased bit space provided by each residual sub data block. The data storage controller generates and adds one or more parity bits and error correction bits to the composite data block for enabling alignment and error correction of the composite data block. In an embodiment, the data storage controller distributes the generated parity bits and error correction bits in the increased bit space of the composite data block over the length of the composite data block. The distribution of the parity bits and error correction bits through the length of the composite data block, for example, results in a reduction in burst errors. In another embodiment, the data storage controller generates distinct index value descriptors for distributing the error correction bits to one or more regions in the programmable data storage device for reducing burst errors. A "region" in a programmable data storage device, for example, a flash memory device is, for example, a memory column associated with the architecture of the programmable data storage device. Furthermore, the data storage controller inserts information on the index value descriptors and the encoding of the transition vectors to the composite data block. In an embodiment, the data storage controller replicates one or more bits of the composite data block to one or more memory locations in the data storage controller for creating data redundancy. These bits comprise, for example, one or more bits of the encoded transition vector in the composite data block.

The composite data block is configurable for writing the composite data block to one or more of multiple regions in the programmable data storage device free from a disturbance caused by a write operation to other regions in the programmable data storage device. As used herein, the term "disturbance" refers to a corruption of bits stored by a programmable cell or an unintended programming of bits on a programmable cell in a particular region in the programmable data storage device resulting from programming of a neighboring region. In an embodiment, the data storage controller skips or masks adjacent regions that are programmable on the programmable data storage device for performing the writing of the composite data block to one or more regions in the programmable data storage device free from the disturbance caused by the write operation to other regions in the programmable data storage device.

In an embodiment, the method and system disclosed herein provides a weight assignment module external to the data

storage controller for assigning weights to one or more regions in the programmable data storage device for distinctly identifying regions free from the disturbance. The assignment of weights is based on, for example, one or more of a location of one or more regions in the programmable data storage device, for example, columns of the flash memory, an organization of programmable cells in the regions, a number of prior write operations performed on the regions, a number of times of movement of bits associated with the regions in the programmable data storage device, etc. The data storage controller configures the composite data block for writing the composite data block to one or more regions in the programmable data storage device by arranging bits of the composite data block according to weights assigned to the regions in the programmable data storage device. In an embodiment, the data storage controller dynamically generates one or more distinct index value descriptors based on weights assigned to the regions in the programmable data storage device for collating bits of the composite data block. The weights distinctly identify one or more regions free from the disturbance. The data storage controller manages storage of the data blocks in 20 the programmable data storage device by organizing the data blocks for each write operation to specific regions in the programmable data storage device and reducing disturbance from writes to other regions in the programmable data storage device without increasing storage size of the programmable 25 data storage device.

In an embodiment, the data storage controller copies the composite data block written to one or more regions in the programmable data storage device to another one or more regions in the programmable data storage device. A decoder 30 in the data storage controller partially decodes the written composite data block based on the dynamically generated distinct index value descriptors. The data storage controller then writes the partially decoded composite data block to the other regions in the programmable data storage device. In an 35 embodiment, the data storage controller performs error correction of the partially decoded composite data block using one or more of the error correction bits in the partially decoded composite data block. The data storage controller deletes the error correction bits of the partially decoded com- 40 posite data block on completion of error correction, prior to writing the partially decoded composite data block to the other regions in the programmable data storage device. In an embodiment, the data storage controller generates and adds one or more distinct error correction bits to the partially 45 decoded composite data block and writes the partially decoded composite data block with the distinct error correction bits to the other regions in the programmable data storage device based on weights assigned to the other regions in the programmable data storage device.

In an embodiment, the data storage controller transmits the partially decoded composite data block to one or more other data storage controllers in communication with the data storage controllers write the received partially decoded composite data block 55 to one or more of multiple regions in their associated programmable data storage devices.

The method and system disclosed herein increases both data retention and the number of times each page in a programmable data storage device can be programmed, without adding to the cost of storage in the programmable data storage device.

# BRIEF DESCRIPTION OF THE DRAWINGS

The foregoing summary, as well as the following detailed description of the invention, is better understood when read in

6

conjunction with the appended drawings. For the purpose of illustrating the invention, exemplary constructions of the invention are shown in the drawings. However, the invention is not limited to the specific methods and components disclosed herein.

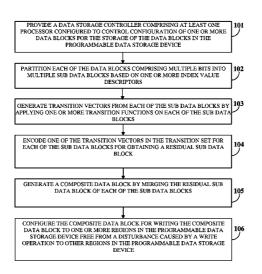

FIG. 1 illustrates a method for managing storage of one or more data blocks in a programmable data storage device.

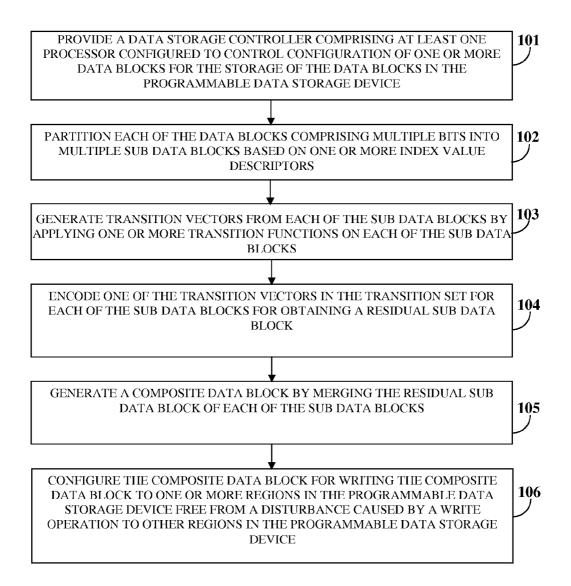

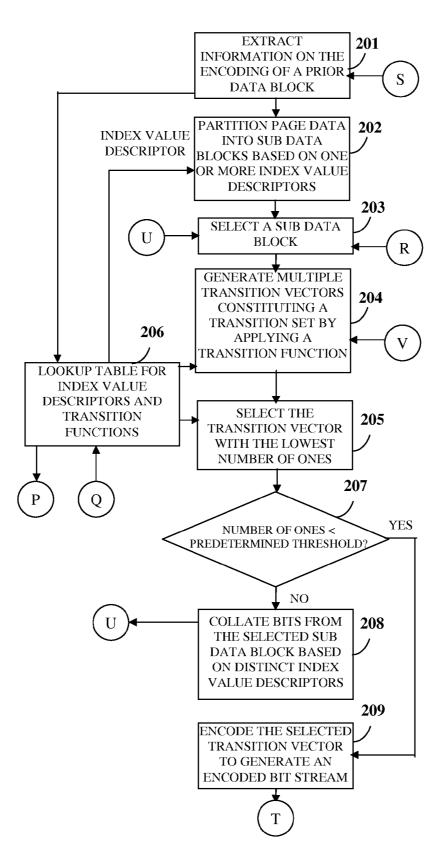

FIGS. 2A-2B exemplarily illustrate a flowchart comprising the steps for managing storage of one or more data blocks in a programmable data storage device using a data storage controller.

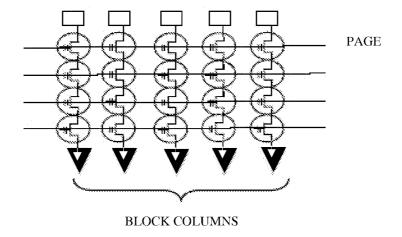

FIG. 3 exemplarily illustrates a data storage array with floating gates in a programmable data storage device.

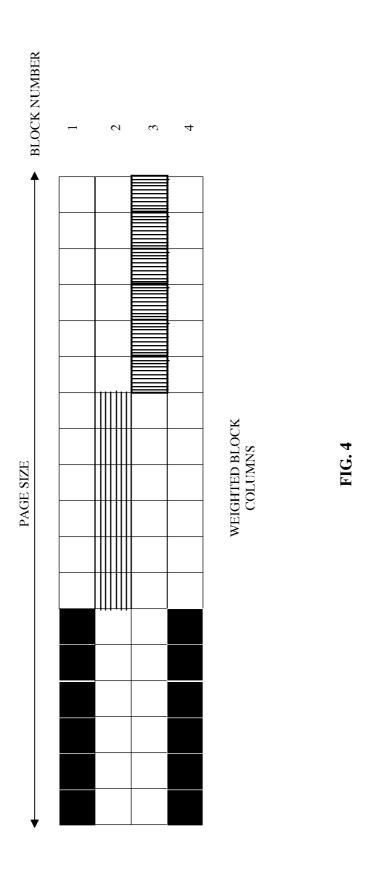

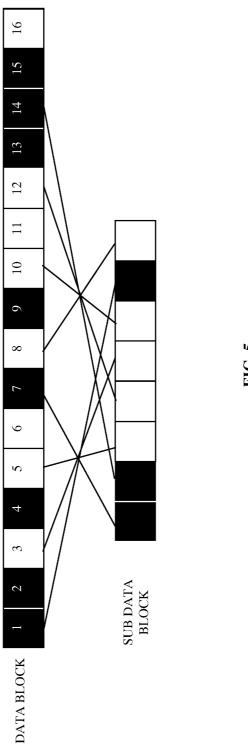

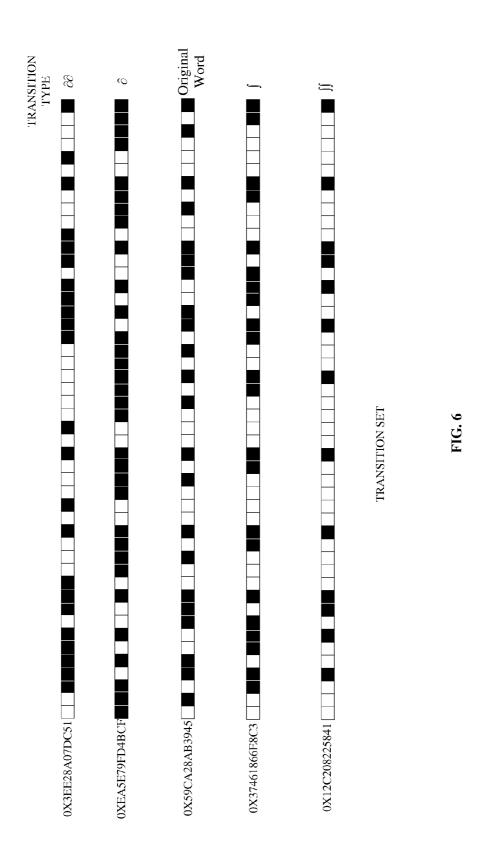

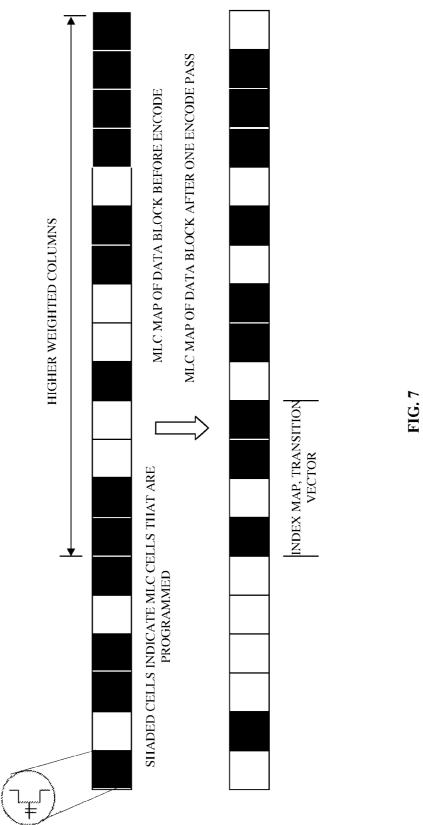

FIGS. **4-7** exemplarily illustrate an encode flow for data blocks to be stored in the programmable data storage device using the data storage controller.

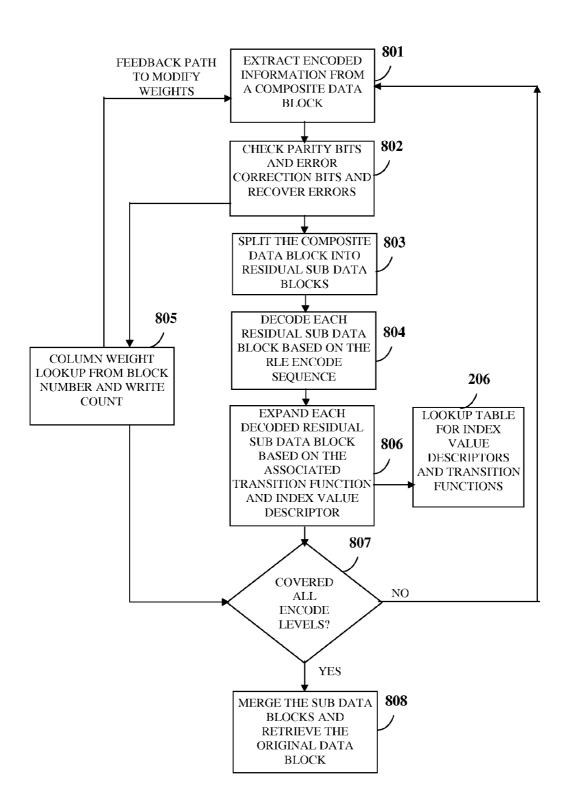

FIG. **8** exemplarily illustrates a flowchart comprising the steps for decoding a composite data block stored in the programmable data storage device to obtain the original data block using the data storage controller.

FIG. 9 exemplarily illustrates an input data block to be configured for storage in a programmable data storage device using the method disclosed herein.

FIG. 10 exemplarily illustrates a data block obtained by merging residual sub data blocks obtained by performing run length encoding according to the method disclosed herein.

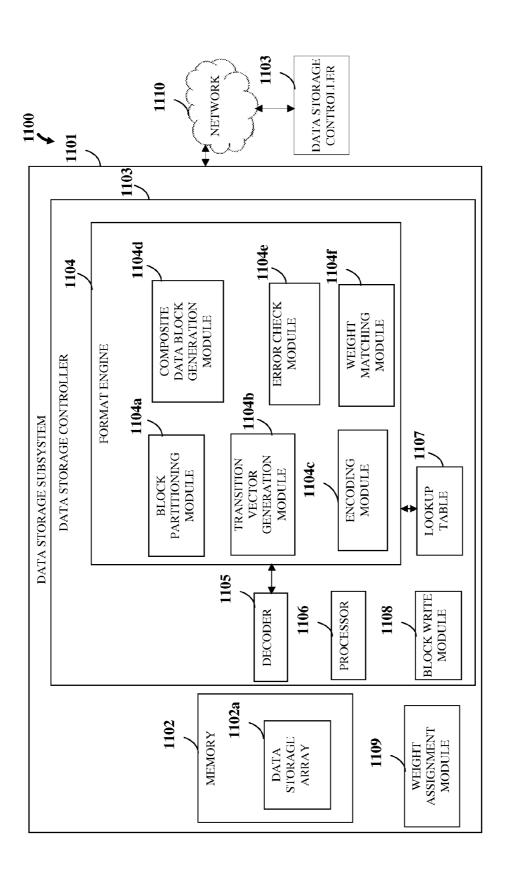

FIG. 11 exemplarily illustrates a system for managing storage of one or more data blocks in a programmable data storage device.

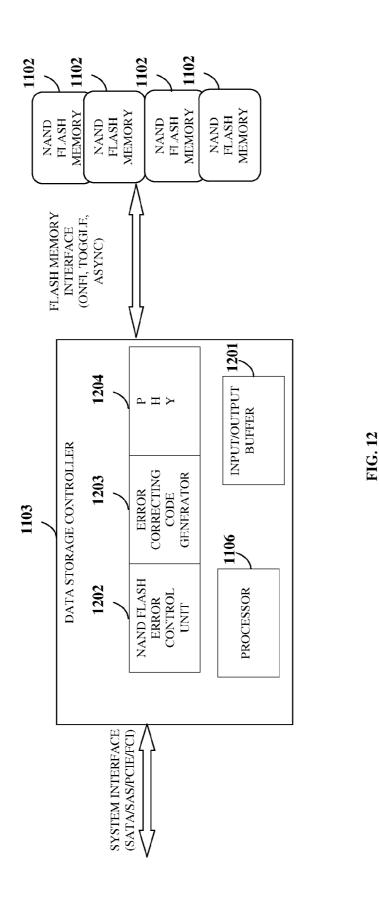

FIG. 12 exemplarily illustrates the architecture of the data storage controller that manages the storage of one or more data blocks in a programmable data storage device.

## DETAILED DESCRIPTION OF THE INVENTION

FIG. 1 illustrates a method for managing storage of one or more data blocks in a programmable data storage device, for example, a flash memory device. The method disclosed herein provides 101 a data storage controller comprising at least one processor configured to control configuration of one or more data blocks for the storage of the data blocks in the programmable data storage device. The data storage controller is, for example, a microcontroller device such as a flash memory controller configured to program the programmable data storage device. In an embodiment, the data storage controller resides inside the programmable data storage device to support movement of pages. The data storage controller partitions 102 each of the data blocks comprising multiple bits into multiple sub data blocks based on one or more index value descriptors. Each of the sub data blocks comprises a distinct sequence of a number of bits. As used herein, the term "index value descriptor" refers to a function that defines a sequence of numbers that determines the order of arrangement of bits extracted from a data block for generating new bit streams for the sub data blocks from the original bit stream of the data block. Each of the numbers is referred to as an index. Each sequence of numbers that determine the order of arrangement of the bits for the sub data blocks is herein referred to as an "index map". A collection of index maps defined by an index value descriptor is herein referred to as "index map set". In an embodiment, the data storage controller is used on smaller partitions of data blocks in multiple iterations to reduce the implementation gate count.

Each index value descriptor defines a particular pattern of partitioning of the data block into sub data blocks. The index value descriptor generates indices, for example, based on prime numbers, consecutive numbers, pseudorandom binary

sequence (PRBS) numbers based on tap points, etc. The indices determine the arrangement of bits from the data block for each of the sub data blocks. Furthermore, in an example, the index value descriptor does not specify all the indices. The data storage controller constructs another sub data block from 5 all the unspecified indices. The index value descriptors reduce the memory space required to store the index maps. The sequence of numbers defined as part of an index map by an index value descriptor is smaller than or equal to the number of bits on which the index value descriptor is applied. The 10 index value descriptors are stored in a lookup table and establish a mapping between the arrangement of bits in the data block and the resultant sub data blocks obtained by partitioning the data block. Each index map is referenced using a sequence number of the index map in the index map set. 15 Furthermore, the data storage controller defines a set of index value descriptors for a data block. The data storage controller selects the index value descriptor based on a prior knowledge about the data block, for example, by determining that the data block is from a moving picture experts group-4 (MPEG- 20 4) file, or selects an arbitrary index value descriptor to initiate partitioning of the data blocks.

In an embodiment, the data storage controller generates index maps for subsequent iterations based on transformations associated with the data block and sub data blocks in a 25 previous iteration. For example, the data storage controller determines that if transition vectors generated for corresponding sub data blocks of a particular data block were encoded in a previous iteration using run length encoding (RLE) of base 2, then the number of sub data blocks is large 30 and consequently, the number of transition vectors in the transition set for the next iteration is larger. The data storage controller checks whether a particular combination of an index map and a transition set comprising the transition vectors enables optimal reorganization of a data block, for 35 example, a moving picture experts group-4 (MPEG-4) data block. If the data storage controller determines that the selected combination of an index map and a transition set does not provide optimal reorganization of a data block, then the data storage controller excludes the combination of that 40 index map and the transition set for subsequent iterations of processing of that data block. In an example, the data storage controller first executes a PRBS based index map for rearranging the bits of the data block before initiating processing on the MPEG-4 data block. The data storage controller gen- 45 erates a sequence of a number of bits in each of the sub data blocks based on the index value descriptors. The data storage controller constructs the sub data blocks such that the sub data blocks are a subset of the original data block and the sequence of bits is determined by the index map.

Consider an example where the data storage controller uses an index map set of length 32, that is, the data storage controller uses 32 index maps. The data storage controller generates a set of unique index maps defined, for example, as an array of prime numbers by an index value descriptor. Therefore, each of the index maps is associated with a corresponding prime number. For an index map "i" in the index map set, the data storage controller extracts a prime number "p" as:

$$p$$

=prime\_number[ $iJ$ . Equation (1)

The prime numbers are stored sequentially in order in an array, that is, as 2, 3, 5, 7, etc. Therefore, the data storage controller determines prime\_number[0] as 2, prime\_number [1] as 3, etc. The length of the array of prime numbers is determined by the length of the index map set. Since the 65 length of the index map set is 32, the data storage controller uses 32 prime numbers for generating 32 possible combina-

8

tions of partitioning the data block into sub blocks. In this example, the data storage controller first partitions the data block into two sub data blocks. The data storage controller determines a first index map as:

$$n_0 = p$$

Equation (2)

For each of the subsequent index maps denoted by  $n_i$  in the index map set, the index map is obtained iteratively as follows:

for

$$(i=1;i < N/2;i++)=n_i=(n_{(i-1)}+p)$$

modulo  $N$ , Equation (3)

where "i" denotes a particular index map, and N denotes the total bit length of the data block. Therefore, each subsequent index map is based on the preceding index map translated by the corresponding prime number and modulo bound by the total number of bits in the data block.

While traversing N/2 bits, the data storage controller tracks the data block as an N bit array. In order to obtain the second data block, the data storage controller generates the complementary N/2 array by complementing the bits from the array generated by Equation (3). In an example, a sub data block resulting from the application of an index value descriptor to a 16 bit data block is exemplarily illustrated in FIG. 5. In another example, the data storage controller uses a pseudorandom binary sequence (PRBS) generator to define the index value descriptors for generating the index maps. The data storage controller generates a PRBS based index value descriptor in order to arrange the bits of the data block more uniformly when one bits herein referred to as "ones" and zero bits herein referred to as "zeros" in a sub data block appear together. This, for example, allows the data storage controller to perform run length encoding (RLE) encoding using a fixed base on the sub data block, since the RLE encoding can be performed optimally when the distribution of ones and zeros is nearly uniform.

Furthermore, in an embodiment, the data storage controller creates data redundancy by replicating the bits of each of the data blocks in one or more of the sub data blocks, during partitioning of each of the data blocks. This ensures that even with the possibility of corruption of one of the sub data blocks, the data storage controller can still retrieve the original data block using the bits replicated in the second sub data block. This allows the data storage controller to regenerate the data block by retrieving the replicated bits. In an example, the data storage controller replicates the bits describing the information on the index value descriptor used for obtaining sub data blocks, to each of the sub data blocks. Therefore, in this example, the data storage controller identifies and selects the bits that operate as a signature for partitioning the data block, that is, the data storage controller selects the bits comprising the information on the index value descriptors, for replication in one or more sub data blocks. This enables the recovery of the original data block in the event of corruption of a particular sub data block.

The data storage controller generates 103 transition vectors from each of the sub data blocks by applying one or more transition functions on each of the sub data blocks. The generated transition vectors constitute a transition set for each of the sub data blocks. As used herein, the term "transition vector" refers to a bit stream comprising bits in a sequence, with a low ratio of ones to zeros or zeros to ones, obtained from a bit stream of the sub data block by application of a transition function. One or more of these bit streams have a lowest possible ratio of ones to zeros or zeros to ones. Also, as used herein, the term "transition function" refers to a reversible mathematical transformation that modifies the bit stream of the sub data block to obtain a bit stream with the desired

ratio of ones to zeros or zeros to ones. Each transition vector of a transition set provides a different pattern of bits for a sub data block. The data storage controller performs one or more reversible mathematical transformations on the distinct sequence of bits in each of the sub data blocks. The reversible 5 mathematical transformation is, for example, a toggle operation such as an exclusive OR (XOR) operation performed on a sub data block. The subsequent transition vectors are generated, for example, by performing a sequence of shift operations and XOR operations on each of the sub data blocks. Therefore, the transition set comprises a collection of toggle vectors or an inverse of the toggle vectors, where a toggle vector is generated by an XOR operation between the bits in a particular sub data block and the bits of the sub data block shifted by a distance parameter that defines the number of bits 15 to be shifted.

The data storage controller stores all the transition vectors in a memory location that is referenced during selection of one of the transition vectors for encoding of the selected transition vector. In an example, the data storage controller 20 stores 8 transition sets in the memory location, where each transition set comprises 16 transition vectors. The first transition set  $T_0$  comprises a collection of transition vectors defined by  $T_{000} T_{002} T_{003} T_{004} T_{005} T_{006} T_{007} T_{008} T_{009} T_{010} T_{011} T_{012} T_{013} T_{014} T_{015}$ . The transition vectors are defined 25 as follows:

$$T_{000}$$

=B, where B is the sub data block. Equation (4)

The data storage controller iteratively generates each of the subsequent transition vectors in the transition set using the 30 transition function below:

for

$$(i=01;i<16;i++)=T_{0i}=T_{0i-1}XOR$$

SHIFT\_LEFT

$$(T_{0i-1})$$

Equation (5)

Therefore, for each transition vector  $T_{0i}$ , the data storage 35 controller performs an exclusive OR (XOR) operation between a previous transition vector  $T_{0i}$ , and a logically left shifted version of the previous transition vector  $T_{0i-1}$  to generate the transition vector  $T_{0i}$ . Furthermore, for generating each of the additional transition sets  $T_1, T_2, T_3, \ldots, T_7$ , the 40 data storage controller uses the equation below:

$$T_j = B XOR SHIFT\_LEFT(B_j + 1)$$

Equation (6)

where XOR SHIFT\_LEFT(B, j+1) is a transition function used to shift a sub data block B by a bit distance "j+1". This 45 generates the first transition vector in the transition set. The data storage controller generates the next 15 transition vectors in the transition set according to equation (5).

The data storage controller stores information on a particular transition set and the consecutive transition vectors in the 50 transition set, for example, in a memory location in the data storage controller. Considering the above example, the data storage controller uses the notation <3 bit group number><4 bit transition vector> where the "group number" refers to the particular transition set to which a transition vector belongs. 55 Therefore, the total number of bits used to encode information on the transition vector is, for example, (3+4) equal to 7 bits.

In an embodiment, the data storage controller selects one of the transition vectors in the transition set based on selection 60 criteria for encoding the selected transition vector. The selection criteria define a cost function for an optimal encoding of a data block. The selection criteria comprise, for example, one of a predetermined ratio of ones to zeros, a lowest number of ones or zeros, a total number of ones lesser than a predetermined threshold, etc. If the data storage controller determines that a transition vector does not have the required ratio of ones

10

to zeros, or zeros to ones, the data storage controller generates new sub data blocks by merging the sub data blocks into groups comprising sub data blocks that meet the selection criteria and the sub data blocks that do not meet the selection criteria. The data storage controller repeats the steps of generating and applying index value descriptors to those sub data blocks that do not meet the selection criteria. In an example, the data storage controller prunes the transition set by selecting transition vectors of the transition set based on an absolute difference in the count of ones and zeros in each transition vector. In another example, the data storage controller prunes the transition set by selecting transition vectors of the transition set with a larger ratio of zeros to ones, and by complementing the ratio of ones to zeros. Therefore, the data storage controller considers all the transition vectors and selects the most desirable pattern of bits to be representative of the sub data block associated with the transition vector, which is used in subsequent encoding steps.

The data storage controller encodes 104 one of the transition vectors in the transition set, that is, the selected transition vector for each of the sub data blocks for obtaining a residual sub data block comprising a reduced number of bits for each of the sub data blocks, resulting in increased bit space for accommodating parity bits and error correction bits. Also, as used herein, the term "bit space" refers to a number of vacant bit positions in a data block. The data storage controller encodes the selected transition vector for each of the sub data blocks, for example, by performing run length encoding (RLE) on the selected transition vector for obtaining the residual sub data block comprising the reduced number of bits for each of the sub data blocks. As used herein, the term "residual sub data block" refers to a sub data block obtained by replacing the original data stream in the selected transition vector with the bit stream having the shortest encode length for the selected transition vector. The data storage controller replaces the bits of each selected transition vector with the encoded bits from the selected transition vector to obtain the residual sub data block. That is, the data storage controller creates the residual sub data block using the bit stream having the shortest encode length obtained by encoding the selected transition vector. The residual sub data block comprises the bits obtained by performing run length encoding on the selected transition vector, the identifiers for the selected index map and the selected transition vector, etc. The residual sub data block further comprises bits used to identify a transformation, for example, an iteration number that identifies a particular iteration of processing.

In an embodiment, the data storage controller parses each of the transition vectors and compares the sequence of bits in each of the transition vectors with predetermined bit patterns. Each of the bit patterns are mapped to an associated encoding string. Therefore, the data storage controller encodes sequences of bits of the selected transition vector that match the predetermined bit patterns according to the associated encoding string, thereby compressing the transition vector and increasing the bit space for obtaining the residual sub data block with increased bit space. The encoding interval of the run length encoding is configured, for example, based on the required ratio of zeros to ones. In an example, the data storage controller first verifies that a transition vector has a fewer number of ones than zeros. The data storage controller performs run length encoding by computing the number of zeros between two ones. If the data storage controller uses a base 2 run length encoding (RLE) then the encoding string "00" corresponds to a scenario where there are no zeros between two ones; the encoding string "01" corresponds to a scenario where there is one zero between two ones; and the encoding

string "10" corresponds to a scenario where there are two zeros between two ones. The encoding string "11" corresponds to a scenario where there are more than two zeros between two ones in which case the data storage controller analyzes the next two bits as well to determine the numbers of 5 zeros between two ones. When the data storage controller uses base 3 RLE, the data storage controller uses 3 bits to represent the number of zeros between two ones. The encoding string "000" represents no zeros and the encoding string "111" represents more than 6 zeros between two ones in 10 which case the data storage controller checks the next 3 bits as well to determine the number of zeros between two ones.

In an embodiment, the data storage controller generates distinct index value descriptors for partitioning each of the sub data blocks for enabling an optimal performance of 15 encoding of one of the transition vectors, that is, the selected transition vector for each of the sub data blocks. This step improves the ratio of zeros to ones for some of the sub data blocks. Furthermore, the data storage controller partitions the sub data blocks to further reduce the number of bits on which 20 the data storage controller performs run length encoding (RLE). This is useful, for example, when the data storage controller needs to reduce the number of bits in the resulting composite data block by only a few bits for a given iteration. Furthermore, the data storage controller also performs parti- 25 tioning of the sub data blocks to improve the efficiency of RLE, since the number of bits saved by further encoding the transition vectors associated with the resulting sub data blocks can be greater than encoding the transition vector associated with the original sub data block.

In an embodiment, the data storage controller partitions all the sub data blocks subsequent to generation of the transition vectors using a set of distinct index value descriptors, generates transition vectors from each of the resulting sub data blocks, and performs run length encoding (RLE) on one of the 35 generated transition vectors selected based on the selection criteria. In an example, the data storage controller generates an index map set comprising multiple index maps according to a selected index value descriptor. The data storage controller performs partitioning of the sub data blocks based on the 40 index maps in the index map set and generates transition vectors from each of the resulting sub data blocks. The data storage controller encodes one of the generated transition vectors for each of the resulting sub data blocks using RLE for obtaining the residual sub data block. The data storage con- 45 troller checks the increase in bit space achieved in each residual sub data block using RLE. If the data storage controller determines that there is no substantial increase in the bit space when compared to the bit space in the original transition vector, the data storage controller does not encode 50 information on the index map along with the encoding information of the original transition vector, and discards the index map used for partitioning the sub data blocks.

The data storage controller generates **105** a composite data block by merging the residual sub data block of each of the 55 sub data blocks. As used herein, the term "composite data block" refers to a data block obtained by combining one or more residual sub data blocks. The composite data block comprises the increased bit space provided by each residual sub data block. The data storage controller generates and adds one or more parity bits and error correction bits, for example, error correcting code (ECC) bits to the composite data block for enabling alignment and error correction of the composite data block. Furthermore, the generation of the parity bits helps maintain the integrity of the encoded words, and adds to 65 the integrity of the page data programmed based on the composite data block in the programmable data storage device.

12

The number of parity bits and/or the error correcting code (ECC) bits added to the composite data block depends on the bit space available after encoding of the transition vectors generated from the sub data blocks in multiple iterations, and the column weights associated with a page to which the composite data block needs to be written in the programmable data storage device. The number of ECC bits is also adapted to match, for example, an expected error rate, a required retention time for a particular page, etc.

The data storage controller inserts information on the encoding of the selected index map, the selected transition vector and the associated transition set, the RLE encoded sequence, etc., to the composite data block. The data storage controller appends, for example, information on a sequence number of the index map in the index map set stored in a memory location of the data storage controller, the index value descriptor stored in the lookup table, the sequence number of the selected transition vector stored in the memory location, the sequence number of the transition function stored in the lookup table, etc., to the composite data block. This information enables decoding of the composite data block for retrieving the original data block. The encoded information can be included either as a prefix or a suffix to the composite data block.

In an embodiment, the data storage controller distributes the generated parity bits and error correction bits in the increased bit space of the composite data block over the length of the composite data block. The distribution of the parity bits and the error correction bits through the length of the composite data block results in a reduction in burst errors. Consider an example where the composite data block is vulnerable to a burst error introduced by the cells of the programmable data storage device. Since the error correction bits are distributed through the length of the composite data block, the data storage controller recovers at least some of the error correction bits that are unaffected by the burst error from the composite data block. The data storage controller further uses the recovered error correction bits to perform error correction on the composite data block and recover the original data block.

In an embodiment, the data storage controller replicates one or more bits of the composite data block to one or more memory locations in the data storage controller for creating data redundancy. These bits comprise, for example, one or more bits of the encoded transition vector in the composite data block. In an embodiment, the data storage controller adds parity bits, error correction bits, etc., to the composite data block and replicates the composite data block along with the parity bits, error correction bits, etc., in the following iteration. The bits comprise a subset of the encoding bits in the composite data block. In an example, the data storage controller replicates bits needed for decoding the composite data block to recover the original data block, for example, the bits representing the sequence of operations performed by the data storage controller to generate the composite data block. The data redundancy ensures that the bits considered essential for recovering the original data block are accessible from at least one memory location.

The data storage controller configures 106 the composite data block for writing the composite data block to one or more of multiple regions in the programmable data storage device free from a disturbance caused, for example, by a write operation of the same composite data block or another data block to other regions in the programmable data storage device. A "region" in a programmable data storage device, for example, a flash memory device, is, for example, a memory column associated with the architecture of the programmable data

storage device. Also, as used herein, the term "disturbance" refers to a corruption of bits stored by a programmable cell or an unintended programming of bits on a programmable cell in a particular region in the programmable data storage device resulting from programming of a neighboring region. Furthermore, storing the composite data block on the programmable data storage device by the data storage controller requires fewer cells to be programmed than storing the original data block.

The configuration of the composite data block for writing 10 of the composite data block to one or more regions in the programmable data storage device comprises arranging bits of the composite data block according to weights assigned to the regions in the programmable data storage device. In an embodiment, the method disclosed herein assigns weights to 15 one or more regions in the programmable data storage device for distinctly identifying regions free from disturbance. The method disclosed herein, for example, provides a weight assignment module external to the data storage controller for assigning the weights to the regions in the programmable data 20 storage device. The weight assignment module is, for example, in electronic communication with the data storage controller. In an embodiment, the weight assignment module is a part of firmware of the data storage controller. In an embodiment, the weight assignment module dynamically 25 generates and assigns the weights to one or more regions in the programmable data storage device, for example, based on one or more of a location of one or more regions in the programmable data storage device, for example, columns of the flash memory, an organization of programmable cells in 30 the regions, a number of prior write operations performed on the regions, a number of times of movement of bits associated with the regions in the programmable data storage device, etc. Furthermore, the weight assignment module assigns the weights, for example, based on memory specifications, num- 35 ber of reads/writes to a particular page, and the retention versus latency requirement associated with a particular write operation. Therefore, the weights distinctly identify one or more regions free from disturbance. In an example, the weight assignment module assigns adjacent columns with 40 mutually exclusive column weights. That is, for every column assigned a weight of 1, the succeeding column is assigned a weight of 0, and vice versa.

In an embodiment, the data storage controller distributes the error correction bits, that is, the error correcting code 45 (ECC) bits to one or more regions in the programmable data storage device based on distinct index value descriptors for reducing burst errors. In an embodiment, the data storage controller dynamically generates one or more distinct index value descriptors based on weights assigned to the regions in 50 the programmable data storage device for collating bits of the composite data block and generating, for example, a modified composite data block. The data storage controller generates the index value descriptors dynamically since the available bit space changes based on each data block written to a page. 55 This means that the number of bits to be programmed to the regions, that is, the columns of the programmable data storage device is not fixed.

Furthermore, the data storage controller dynamically generates index value descriptors that define index maps according to the weights assigned to one or more regions in the programmable data storage device, for example, the column weights. The index maps define the distribution of the error correction bits and/or the parity bits through the regions in the programmable data storage device according to the column weights. The index value descriptors define index maps that arrange the bits of the composite data block to ensure the

14

assignment of the error correcting code (ECC) bits and/or the parity bits to columns with the largest weight, for example, columns associated with a weight of one. The column weights define the selected columns, for example, those columns that are less vulnerable to disturbance, to be programmed for a particular page. In an example, the data storage controller assigns a larger weight to the selected columns. Therefore, if the data storage controller determines that the number of bits to be stored in the programmable data storage device is lower than the number of columns assigned with larger weights, then the data storage controller uses only the columns assigned with larger weights for performing the write operation. If the data storage controller determines that the number of columns assigned with larger weights is less than the number of bits from the composite data block to be written to the programmable data storage device, that is, the total number of bits obtained after adding ECC and/or parity bits to the composite data block, the data storage controller assigns the ECC and/or parity bits with a greater preference than the other bits of the composite data block, for writing to the columns with larger weights. When the number of columns assigned with larger weights is greater than the number of bits in the composite data block, the data storage controller toggles the bits of the composite data block and writes the toggled bits to the unfilled columns. Therefore, the larger column weights instruct the data storage controller to program specific columns of a particular page in the programmable data storage device.

The data storage controller accesses the weights assigned to each of the regions, for example, the weights assigned to the columns for each row by the weight assignment module for overcoming the disturbance caused by the write operation. During the programming of the composite data block to a row on the programmable data storage device, the data storage controller analyzes the weights assigned to each of the columns associated with that row and writes the bits of the composite data block into the columns with a lower weight less often. This reduces the effect of the disturbance caused by the write operation to other regions in the programmable data storage device.

The data storage controller aligns the composite data block based on the weights assigned to the regions in the programmable data storage device, for example, based on the weights assigned to the columns to be written. The data storage controller generates and adds one or more parity bits to the composite data block for storing the aligned composite data block in the programmable data storage device. Furthermore, the data storage controller fills the composite data block with zeros to match the selected columns. For example, the data storage controller fills the composite data block with zeros to arrange the bits to match the columns assigned with larger weights. That is, the data storage controller assigns a greater preference to columns with larger weights for writing to the programmable data storage device. If the data storage controller determines that the composite data block has a lower number of bits than the number of columns assigned with larger weights, then the data storage controller sets additional zeros to program the selected columns. The data storage controller thereby manages storage of the data blocks in the programmable data storage device by organizing the data blocks for each write operation to particular regions in the programmable data storage device and reducing disturbance from write operations to other regions in the programmable data storage device without increasing the storage size of the programmable data storage device.

The data storage controller minimizes the number of data blocks that go through program erase cycles for each write

operation, while minimizing the effect of disturbance caused during programming of the regions, for example, the columns in the programmable data storage device, by a write operation to other columns in the programmable data storage device. The distribution of programmable cells is controlled across 5 multiple write operations to a page of the programmable data storage device using column weights that change along with the write count, that is, the number of write operations to a location in the programmable data storage device, for the composite data block. The weights assigned to a column of a 10 programmable cell are configured to cluster the programmable cells to specific locations of the page. To uniformly use the available cells in a page, weights are moved after each page is erased. In an embodiment, the weights assigned to a column are modified based on the number of previous write 15 operations associated with the pages that are programmed with the composite data block. The encoded data blocks are aligned with the column weights after the iterations. The alignment is used to calculate the number of additional parity bits that are to be added to the composite data block.

In an embodiment, the data storage controller skips or masks adjacent regions that are programmable on the programmable data storage device for writing the composite data block to one or more regions in the programmable data storage device free from disturbance caused by a write operation 25 to other regions in the programmable data storage device. For example, the clustering effect around weighted columns can be used to reduce the program time for a page by masking regions. Moreover, skipping continuous columns of a page by the data storage controller reduces the write time or program 30 time. Furthermore, in an embodiment that enables faster data recovery, the data storage controller writes the error correcting code (ECC) bits to separate locations equipped to hold ECC bits to correct bit errors in a page of the programmable data storage device. In an embodiment, the data storage con- 35 troller uses, for example, low density parity check (LDPC) codes for error correction without additional bit space overhead. Therefore, in the method disclosed herein, the location and number of parity bits are determined in conjunction with the operations of the data storage controller to reduce the 40 number of programmed cells and skew the programmed cells resulting in an increase of the number of parity bits that are included in the composite data block.

In an embodiment, the data storage controller copies the composite data block written to one or more regions in the 45 programmable data storage device to other regions in the programmable data storage device. A decode of the data storage controller partially decodes the composite data block written to one or more regions in the programmable data storage device based on the dynamically generated distinct 50 index value descriptors. For example, when the composite data block is moved between pages in the same programmable data storage device or between different programmable data storage devices, the decoder performs only a partial decode of the written composite data block. In order to 55 generate the partially decoded composite data block, the data storage controller reverses only some of the steps of encoding of the composite data block. The data storage controller, for example, retrieves the composite data block from a modified composite data block, by reversing the step of generating the 60 index maps based on the column weights. The data storage controller removes the column weights because different pages have different column weights. In an embodiment, the data storage controller accesses the column weights stored in a lookup table for performing the partial decoding of the 65 composite data block. Therefore, the data storage controller enables the copying of the composite data block across loca16

tions in the programmable data storage device without completely decoding the composite data block. The data storage controller then writes the partially decoded composite data block to other regions in the programmable data storage device.

In an embodiment, the data storage controller performs error correction of the partially decoded composite data block using one or more of the error correction bits in the partially decoded composite data block. The data storage controller deletes one or more of the error correction bits of the partially decoded composite data block on completion of the error correction, prior to writing the partially decoded composite data block to the other regions in the programmable data storage device. This reduces the bandwidth required for copying the composite data block to other regions in the programmable data storage device. Furthermore, the data storage controller provides separate error protection for every copy of the composite data block to other regions in the programmable data storage device, or transmission of the composite data 20 block to other data storage controllers that configure composite data blocks for writing to their associated programmable data storage devices. The data storage controller generates and adds one or more distinct error correction bits to the partially decoded composite data block and writes the composite data block with the distinct error correction bits to the other regions in the programmable data storage device based on weights assigned to the other regions in the programmable data storage device.

In an embodiment, the data storage controller transmits the partially decoded composite data block to one or more other data storage controllers in communication with the data storage controller via a network. The network is, for example, a local area network, a communication network implementing WiFi® of the Wireless Ethernet Compatibility Alliance, Inc., a Bluetooth® communication network, a wireless universal serial bus (USB) communication network, etc. The other data storage controllers write the received partially decoded composite data block to one or more regions in their associated programmable data storage devices. In an application of the method disclosed herein, the composite data block can be transmitted across different storage devices to reduce the memory wear on the storage device to which the composite data block is copied. The receiving programmable data storage device can, for example, further iteratively process this composite data block to reduce errors and improve error recovery.

The data storage controller performs the partitioning of the data blocks to sub data blocks, generation of the transition vectors, and encoding of the selected transition vectors recursively during each successful copy or write operation for each of the data blocks. The data storage controller performs multiple iterations of each of these steps after generating the composite data block with the encoded bits and the associated parity bits and error correction bits to create larger bit spaces for alignment, error correction, etc.

The data storage controller decodes the composite data block to obtain the original data block using the information on the selected index maps, the selected transition vector, the RLE encode sequence, etc. The data storage controller recovers the errors in the data of the composite data block by performing error correction using the error correcting code (ECC) bits. The data storage controller performs a reversible mathematical transformation on the transition vector to retrieve the data of the original sub data block, expands each of the sub data blocks based on the index maps, and merges the sub data blocks to retrieve the original data block as disclosed in the detailed description of FIG. 8.

The data storage controller can be used in different ways over the life cycle of the programmable data storage device. When the programmable data storage device is new, the data storage controller writes into most of the columns, that is, the data storage controller cycles through a number of programmable cells to improve write speed. As the number of writes to a page in the programmable data storage device increases, the data storage controller adapts the programming of the cells in order to write fewer bits, and to skew the redundant bits inside a page. If one or more columns have developed an error, the data storage controller excludes the columns from the write operations without compromising data.

FIGS. 2A-2B exemplarily illustrate a flowchart comprising the steps for managing storage of one or more data blocks in a programmable data storage device using a data storage 15 controller. The data storage controller extracts 201 information on the encoding of a prior data block. The data storage controller analyzes this information to obtain the sequence number of the most recently used index map, the individual weights used for programming the memory columns, the 20 block number and location, etc., of the previous composite data block. The data storage controller then accesses the lookup table 206 to extract index value descriptors. The data storage controller partitions 202 the page data into sub data blocks based on one or more index value descriptors and 25 generates a sequence of bits based on the index value descriptors. The data storage controller selects 203 a sub data block. The data storage controller then generates 204 multiple transition vectors constituting a transition set by applying a transition function on the selected sub data block.

The data storage controller generates the transition vectors based on a set of transition functions. In this example, the data storage controller performs an exclusive OR (XOR) operation on each of the sub data blocks to obtain a respective first transition vector. The data storage controller then generates 35 consecutive transition vectors for each of the sub data blocks, for example, using equation (5) as disclosed in the detailed description of FIG. 1. The data storage controller stores each of the resultant transition vectors for each of the sub data blocks in a memory location, thereby compiling a list of 40 possible bit sequences that can be encoded. The data storage controller then accesses the memory location and selects 205 the transition vector with the lowest number of one bits, herein referred to as "ones". The data storage controller checks 207 whether the number of ones in the selected tran- 45 sition vector is less than a predetermined threshold of a number of ones for a particular length of a data block. If the number of ones in the selected transition vector is lesser than the predetermined threshold, the data storage controller proceeds to encode 209 the selected transition vector to generate 50 an encoded bit stream. In this example, the data storage controller performs RLE encoding on the selected transition vector. If the data storage controller determines that the number of ones in the selected transition vector is greater than the predetermined threshold, the data storage controller collates 55 bits from the selected sub data block based on distinct index value descriptors. The data storage controller accesses the lookup table 206 for distinct index value descriptors based on which the data storage controller collates 208 bits from the selected sub data block and performs further partitioning of 60 the selected sub data block. The data storage controller further selects 203 one of the resulting sub data blocks and generates 204 multiple transition vectors constituting a transition set by applying a transition function to the selected sub data block. Furthermore, the data storage controller continues to reorganize each of the sub data blocks before every write operation to the programmable data storage device for a pre18

determined number of iterations. The data storage controller sets the number of iterations based on the latency tolerance of the write operation. For example, since a wear leveling write operation is configured with a tolerance to a greater latency, the data storage controller sets a greater number of iterations when using wear leveling.

After encoding each selected transition vector to generate an encoded bit stream, the data storage controller checks 210 whether all the transition functions defined for a data block have been applied by accessing the lookup table 206. If all the transition functions have been applied to each sub data block, the data storage controller collects all the encoded bit streams generated from the encoding of the transition vectors. If all the transition functions defined for a data block have not been applied, the data storage controller applies the transition functions accessed from the lookup table 206 to generate 204 transition vectors and repeats the steps 205, 207, 208, and 209 for generating corresponding encoded bit streams.